# Multiplying Polynomials without Powerful Multiplication Instructions (Long Paper)

Vincent Hwang<sup>1</sup>, YoungBeom Kim<sup>2</sup> and Seog Chung Seo<sup>2</sup>

<sup>1</sup> Max Planck Institute for Security and Privacy, Bochum, Germany vincentvbh7@gmail.com

<sup>2</sup> Kookmin University, Seoul, Korea darania@kookmin.ac.kr, scseo@kookmin.ac.kr

**Abstract.** We improve the performance of lattice-based cryptosystems Dilithium on Cortex-M3 with expensive multiplications. Our contribution is two-fold: (i) We generalize Barrett multiplication and show that the resulting shape-independent modular multiplication performs comparably to long multiplication on some platforms without special hardware when precomputation is free. We call a modular multiplication "shape-independent" if its correctness and efficiency depend only on the magnitude of moduli and not the shapes of the moduli. This was unknown in the literature even though modular multiplication has been studied for more than 40 years. In the literature, shape-independent modular multiplications often perform several times slower than long multiplications even if we ignore the cost of the precomputation. (ii) We show that polynomial multiplications based on Nussbaumer fast Fourier transform and Toom–Cook over  $\mathbb{Z}_{2^k}$  perform the best when modular multiplications are expensive and k is not very close to the arithmetic precision.

For practical evaluation, we implement assembly programs for the polynomial arithmetic used in the digital signature Dilithium on Cortex-M3. For the modular multiplications in Dilithium, our generalized Barrett multiplications are 1.92 times faster than the state-of-the-art assembly-optimized Montgomery multiplications, leading to 1.38-1.51 times faster Dilithium NTT/iNTT. Along with the improvement in accumulating products, the core polynomial arithmetic matrix-vector multiplications are 1.71-1.77 times faster. We further apply the FFT-based polynomial multiplications over  $\mathbb{Z}_{2^k}$  to the challenge polynomial multiplication  $ct_0$ , leading to 1.31 times faster computation for  $ct_0$ .

We additionally apply the ideas to Saber on Cortex-M3 and demonstrate their improvement to Dilithium and Saber on our 8-bit AVR environment. For Saber on Cortex-M3, we show that matrix-vector multiplications with FFT-based polynomial multiplications over  $\mathbb{Z}_{2^k}$  are 1.42-1.46 faster than the ones with NTT-based polynomial multiplications over NTT-friendly coefficient rings. When moving to a platform with smaller arithmetic precision, such as 8-bit AVR, we improve the matrix-vector multiplication of Dilithium with our Barrett-based NTT/iNTT by a factor of 1.87-1.89. As for Saber on our 8-bit AVR environment, we show that matrix-vector multiplications with NTT-based polynomial multiplications over NTT-friendly coefficient rings are faster than polynomial multiplications over  $\mathbb{Z}_{2^k}$  due to the large k in Saber.

**Keywords:** Lattice-based cryptography · Dilithium · Saber · Barrett multiplication · Microcontroller · Nussbaumer FFT · Toom–Cook

## 1 Introduction

At PQCrypto 2016, the National Institute of Standards and Technology (NIST) announced the Post-Quantum Cryptography Standardization soliciting standards on post-quantum

cryptography. Among various candidates, lattice-based cryptosystems usually exhibit reasonably balanced public key, secret key, ciphertext, and signature sizes. In most lattice-based cryptosystems, the designers choose between several algebraic structures while considering various implementation considerations. In the specifications of Kyber [ABD+20b], a key encapsulation mechanism standardized by NIST, and Dilithium [ABD+20a], a digital signature standardized by NIST, the authors wrote specific number-theoretic transforms (NTTs) over the so-called "NTT-friendly" primes to the schemes due to the quasi-linear algebraic complexity of multiplying polynomials with NTTs. On the other hand, the authors of Saber [DKRV20], a 3rd round KEM finalist, argued the efficiency of computing modulo a power of two while resorting to Toom–Cook and Karatsuba with less performant asymptotic runtime.

The software performance of polynomial multiplications has been extensively studied. On high-end processors, [Sei18, CHK+21, NG21, SKS+21a, SKS21b, BBCT22, BHK+22b, BMK+22, ORGF+22, ZHS+22, CCHY24, HLY24, Hwa24a] studied the interactions between algebraic structures and vectorization. On low-end processors and platforms, [KRS19, BKS19, MKV20, IKPC20, GKS21, ACC+21, CHK+21, ACC+22, IKPC22, AHY22] studied various aspects of microcontroller implementations, including performance cycles, memory usage, code size, and more. In these works, the designs of polynomial multipliers consist of (i) specific approaches implementing modular multiplications with the designated instruction set architectures/extensions and (ii) specific fast transformations converting the large multiplication tasks into several small multiplication tasks.

In the literature, there are many popular lines of modular multiplications. We call a modular multiplication "shape-independent" if its correctness and efficiency depend only on the magnitude of moduli and not the shapes of the moduli. There are three lines of shape-independent modular multiplications computing representatives of ab modulo q with precomputations – Montgomery, Barrett, and Plantard. Montgomery multiplication computes the modular product as the high part of the sum of long products [Mon85, Sei18]. Recently, [Pla21] proposed the unsigned Plantard multiplication using integer middle products, an operation that is no cheaper than a high multiplication  $^1$ . The idea was later adapted to the signed version by [HZZ<sup>+</sup>22] using special multiplication instructions unseen on most of the architectures and by [AMOT22] using multiplication instructions with twice the precision. Montgomery multiplication amounts to computing two long/high multiplications and one low multiplication, and Plantard multiplication amounts to computing one middle product and one long/high multiplication. This work proposes a shape-independent modular multiplication that performs comparably to a long multiplication on some platforms without special hardware. We rely on two observations:

- Barrett multiplication: Barrett multiplication computes the modular product with one high multiplication and two low multiplications [Sho, BHK<sup>+</sup>22b].

- Approximation nature of the high multiplication: In Barrett multiplication, the high multiplication only needs to be approximately correct in contrast to Montgomery and Plantard multiplications.

Contribution 1: We generalize the notion of approximation that is suitable for approximating the high multiplication with multi-limb arithmetic and show that the resulting generalized Barrett multiplication performs comparably to long multiplication on our platform, defying the expectation that modular multiplication, such as Montgomery and Plantard multiplications, must amount to a long multiplication followed by non-negligible computations. To the best of our knowledge, this is the first time that shape-independent modular multiplication performs comparably to long

<sup>&</sup>lt;sup>1</sup>Formally, one can implement a high multiplication with a middle product, so the cost of one middle product cannot be cheaper than one high multiplication.

multiplication on a platform like Cortex-M3 with a relatively simple cost model, even though people have been studying modular multiplications for more than 40 years. We also believe that our Barrett multiplication performs the best on other Cortex-M processors, such as Cortex-M0, Cortex-M0+, and Cortex-M23, with similar characteristics.

The second part of the paper challenges the notion of "NTT-friendliness" of coefficient rings in practice. Although FFT/NTT-based polynomial multiplication over arbitrary rings was already known more than 20 years ago [CK91], several recent works presented NTTs in severely restricted forms. NTT was usually presented as a fast transformation over an "NTT-friendly" coefficient ring  $\mathbb{Z}_q$  for an odd q. In fact, NTTs can be defined over unital and possibly non-commutative rings by manufacturing various "NTT-friendly" structures while extending the polynomial rings.

Contribution 2: We propose a polynomial multiplier based on Nussbaumer FFT and Toeplitz matrix-vector product built upon Toom-4 over  $\mathbb{Z}_{2^k}$ , and show that the resulting implementation performs the best when k is not very close to the arithmetic precision. To the best of our knowledge, this is the first implementation of FFT-based polynomial multipliers over  $\mathbb{Z}_{2^k}$ . On the other hand, if k is close to the arithmetic precision, we show that NTT-based polynomial multiplications over NTT-friendly coefficient rings perform the best.

Our results bring insights into the impact of coefficient rings on polynomial multiplications. If the coefficient ring is an NTT-friendly one modulo a prime and the corresponding long/high multiplications are slow, then one should use Barrett multiplication instead of Montgomery multiplication. On the other hand, if the coefficient ring takes the form  $\mathbb{Z}_{2^k}$  and k is small enough, FFT-based polynomial multiplication over  $\mathbb{Z}_{2^k}$  performs the best; and when k is large, the standard NTT-based approach over NTT-friendly coefficient rings performs the best.

Applications and limitations of our Barrett multiplications. For a positive integer n, we identify  $\mathbb{Z}_n := \left[-\frac{n}{2}, \frac{n}{2}\right) \cap \mathbb{Z}$  and define the map  $\mathrm{mod}^{\pm}n$  as the function mapping an integer z to the element in  $\mathbb{Z}_n$  differing by a multiple of n. Let R be a power of two with exponent a power of two,  $\log_2 \mathtt{R}$  be the arithmetic precision, q be an odd modulus with  $\sqrt{R} < q < R$ . For two integers  $a, b \in \mathbb{Z}_R$ , this work studies the computation of a representative  $c \in \mathbb{Z}_R$  of ab modulo q. In practice, a modular multiplication usually admits an integer B with  $q \leq B \leq R$  such that  $c \in \mathbb{Z}_B$ . We study the relations between the efficiency of modular multiplications and the magnitude of q and B, and do not exploit the structure of q other than being an odd integer<sup>2</sup>. In terms of the definability of shape-independent modular multiplications, Barrett, Montgomery, and Plantard multiplications compute a representative  $c \in \mathbb{Z}_{B}$  of ab modulo q with a pre-modular-multiplication by a constant in the Barrett case and a post-modular-multiplication by a constant in the Montgomery and Plantard cases. In our context, we focus on the 32-bit modular multiplications ( $R = 2^{32}$ ) in the Dilithium NTT/iNTT computations, where pre-modular-multiplications are carried out during the design phase rather than the computation phase. By relaxing the worst-case<sup>3</sup> of B to be five times larger than prior signed Barrett multiplication [BHK+22b], our generalized signed Barrett multiplication outperforms any other modular multiplications consisting of at least one high/long multiplication and non-negligible pre-/post-computation on Cortex-M3,

$<sup>^{2}</sup>$ In fact, Barrett multiplication works when q is even, but the resulting computation requires a slightly more involved justification and does not find applications in our context.

<sup>&</sup>lt;sup>3</sup>By worst case, we mean the theoretical worst-case analysis, which does not imply that the resulting bound is attainable. The new bound B could be smaller than the theoretical worst-case analysis in practice. Typically, brute-force testing with ball analysis will reveal a much better bound. In this paper, we stick to the theoretical worst-case analysis since the bound is much more modular than the brute-force approach.

including Montgomery and Plantard multiplications as well as other approaches applying specialized modular reductions to the long products. Furthermore, we also show that our generalized Barrett multiplication only reduces the bit-sizes of valid moduli from 28.1926 to 26.0458 for an 8-layer 32-bit NTT with only the necessary modular multiplications.

Source code. Our source code is publicly available at https://github.com/vincentvbh/PolyMul Without PowerfulMul.

# 2 Preliminiaries

# 2.1 Integer Approximation

For a function  $[]]: \mathbb{R} \to \mathbb{Z}$ ,  $[BHK^+22b]$  call it an integer approximation if  $\forall r \in \mathbb{R}, |r-[r]| \le 1$ . Common examples are the floor function  $\lfloor \rfloor$ , ceiling function  $\lceil \rceil$ , and rounding-half-up function  $\lfloor \rceil$ .  $[BHK^+22b]$  chose  $\lfloor \rceil_2 := r \mapsto 2 \lfloor \frac{r}{2} \rfloor$  and demonstrated its benefit for the vector instruction set Neon in Armv8-A. It is easily seen that  $\lfloor \rfloor, \lceil \rceil, \lfloor \rceil, \lfloor \rceil_2$  are all integer approximations.

# 2.2 Modular Multiplications

Throughout this paper, we consider  $\mathbf{R}=2^{32}$  and  $q<\mathbf{R}$  an odd number, and focus on signed arithmetic. For an integer approximation  $[\![]\!]$ , we define the corresponding modular reduction  $\mathrm{mod}^{[\![]\!]}q:\mathbb{Z}\to\mathbb{Z}$  as  $\mathrm{mod}^{[\![]\!]}q\coloneqq z\mapsto z-\left[\![\frac{z}{q}]\!]q$ . Furthermore, we define  $|\mathrm{mod}^{[\![]\!]}q|\coloneqq \mathrm{max}_{z\in\mathbb{Z}}|z\bmod^{[\![]\!]}q$ . If  $[\![]\!]=\lfloor \rceil$ , we denote  $\mathrm{mod}^{\lfloor \rceil}$  as  $\mathrm{mod}^{\pm}$ .

**Arithmetic modulo**  $R = 2^m$ . In most modern platforms, since elements are usually presented as bit strings with power-of-two bits, arithmetic modulo a power of two  $R = 2^m$  with m a power of two attributes to straightforward quantification of performance cycles. For two m-bit integers a and b, we call an instruction long multiplication if it computes the 2m-bit result ab. If an instruction computes a value sufficiently close to the upper m bits of ab, we call it a high multiplication. Further, we call an instruction low multiplication if it computes a value sufficiently close to the lower m bits of ab. For simplicity, we also call the subtractive and accumulative variants long, high, and low multiplications.

**Montgomery multiplication.** Let  $a,b\in\left[-\frac{\mathtt{R}}{2},\frac{\mathtt{R}}{2}\right]$  be two m-bit integers. Montgomery multiplication computes a representative of  $ab\mathtt{R}^{-1}$  mod q with two long multiplications and one low multiplication as shown in Algorithm 1. Intuitively, we first compute a value c satisfying  $c\equiv 0\pmod{\mathtt{R}},\ c\equiv ab\pmod{q}$ , and  $|c|<|ab|+\frac{\mathtt{R}q}{2}$ . Since  $\frac{c}{\mathtt{R}}$  is an integer and  $\mathtt{R}$  is coprime to q, we have  $\frac{c}{\mathtt{R}}\equiv ab\mathtt{R}^{-1}\pmod{q}$ .

**Barrett multiplication.** Barrett multiplication was first introduced only in the reduction form, reducing a value by subtracting a reasonably approximated multiple of q [Bar86]. [Sho] proposed the multiplicative form for unsigned arithmetic, and [BHK<sup>+</sup>22b] proposed the signed multiplication with integer approximations as shown in Algorithm 2. [BHK<sup>+</sup>22b] computed a representative of  $ab \mod q$  by pulling the operand b to the approximation and showed that the result is an m-bit value by establishing a correspondence between Barrett and Montgomery multiplications and reusing the bound from Montgomery multiplication.

Algorithm 1 Montgomery multiplication.tion.Inputs:

$$a, b$$

.Output:  $c \equiv ab \operatorname{R}^{-1} \operatorname{mod} {}^{\pm}q$ .Output:  $c \equiv ab \operatorname{R}^{-1} \operatorname{mod} {}^{\pm}q$ .1:  $tlo = a \cdot b \operatorname{mod} {}^{\pm}R$ 1:  $tfull = a \cdot b$ 2:  $tlo = tfull \operatorname{mod} {}^{\pm}R$ 2:  $tlo = tfull \operatorname{mod} {}^{\pm}R$ 2:  $thi = \left\lfloor \frac{a \cdot \left\lfloor \frac{bR}{q} \right\rfloor}{R} \right\rfloor$ 3:  $q' = -q^{-1} \operatorname{mod} {}^{\pm}R$ 3:  $c = tlo - (thi \cdot q \operatorname{mod} {}^{\pm}R)$ 5:  $tfull = tfull + tlo \cdot q$ 6:  $c = \left\lfloor \frac{tfull}{R} \right\rfloor$

A correspondence between Barrett and Montgomery multiplications.  $[BHK^+22b]$  showed that for an integer approximation [], we have

$$ab - \left\lfloor \frac{a\left[\left[\frac{b\mathbb{R}}{q}\right]\right]}{\mathbb{R}}\right\rceil q = \frac{a\left(b\mathbb{R} \bmod \mathbb{I} q\right) + \left(a\left(b\mathbb{R} \bmod \mathbb{I} q\right)\left(-q^{-1}\right) \bmod {}^{\pm}\mathbb{R}\right)q}{\mathbb{R}}.$$

Their proof clearly transfers to the following generalization: For integer approximations  $[]_0, []_1$ , we have

$$ab - \left[ \left[ \frac{a \left[ \left[ \frac{b\mathbf{R}}{q} \right] \right]_{0}}{\mathbf{R}} \right] \right]_{1} q = \frac{a \left( b\mathbf{R} \bmod \mathbb{I}_{0} q \right) + \left( a \left( b\mathbf{R} \bmod \mathbb{I}_{0} q \right) \left( -q^{-1} \right) \bmod \mathbb{I}_{1} \mathbf{R} \right) q}{\mathbf{R}}.$$

Applying the correspondence, we have

$$\left|ab - \left[\!\left[\frac{a\left[\!\left[\frac{bR}{q}\right]\!\right]_{0}}{R}\right]\!\right]_{1}q\right| \leq \frac{|a| \mid \operatorname{mod} \left[\!\left[0\right]_{0}q\right| + \mid \operatorname{mod} \left[\!\left[1\right]_{1}R\right|q}{R}$$

. When  $\left[\!\left[0\right]_{0} = \left[\!\left[0\right]_{1}\right]_{1} = \left[\left[1\right]_{1}$ , we have  $\left|ab - \left[\!\left[\frac{a\left[\!\left[\frac{bR}{q}\right]\!\right]_{0}}{R}\right]\!\right]_{1}q\right| \leq \frac{q}{2}\left(1 + \frac{|a|}{R}\right)$ .

#### 2.3 Number Theoretic Transform

Let R be a commutative ring with identity. For an n-th root of unity  $\omega_n \in R$ , we call  $\omega_n$  principal if  $\forall j = 1, \ldots, n-1, \sum_{i=0}^{n-1} \omega_n^{ij} = 0$ . If there is a principal n-th root of unity for a large n, we call R an "NTT-friendly" coefficient ring. In this paper, we only consider n a power of two, whose condition is equivalent to  $\omega_n^{\frac{n}{2}} = -1$  [Für09, Lemma 2.1]. For an invertible element  $\zeta \in R$ , we have the following isomorphism by the Chinese remainder theorem for polynomial rings:

$$\frac{R[x]}{\langle x^n - \zeta^n \rangle} \cong \prod \frac{R[x]}{\langle x^{\frac{n}{2}} \pm \zeta^{\frac{n}{2}} \rangle} \cong \cdots \cong \prod_{i_0, \dots, i_{\log_2 n - 1} = 0, 1} \frac{R[x]}{\langle x - \zeta \omega_n^{\sum_j i_j 2^j} \rangle}.$$

This is the radix-2 Cooley–Tukey FFT for a discrete weighted transform [CT65, CF94]. We call  $\zeta = \omega_n$  the cyclic case and  $\zeta = \omega_{2n}$  the negacyclic case, and illustrate the idea in Figure 1. If  $R = \mathbb{Z}_{2^{2^t}+1}$ , this is called Fermat number transform (FNT) since  $2^{2^t}+1$  is a Fermat number [SS71, AB74]. There are several benefits while operating in this coefficient ring. First of all, since  $2^{2^t} = -1 \in \mathbb{Z}_{2^{2^t}+1}$ , we have 2 a principal  $2^{t+1}$ -th root of unity for Cooley–Tukey FFT. This improves the performance of twiddle factor multiplications since multiplications by powers of two are fast [SS71, AB74, AHKS22, BHK<sup>+</sup>22a]. The second benefit is the efficient modular reduction [SS71, AHKS22, BHK<sup>+</sup>22a].

Figure 1: NTT and its inverse over  $x^8 - 1$  and  $x^4 + 1$ .  $\omega_n = \omega^{8/n}$  where  $\omega$  is a principal 8th root of unity, adapted from [ACC<sup>+</sup>22]. Computational flow goes from left to right.

# 2.4 Nussbaumer Fast Fourier Transform

Nussbaumer fast Fourier transform manufactures algebraic structures suitable for NTT-based algebra homomorphisms, and the resulting transformation requires only additions and subtractions [Nus80]. For simplicity, we illustrate the idea when the polynomial modulus is a power-of-two cyclotomic polynomial.

The goal is to design fast transformations for the ring  $R[x]/\langle x^n+1\rangle$  with only additions and subtractions in R where  $n=2^k$ . Conceptually, we chop a size-n polynomial into  $\Theta\left(\sqrt{n}\right)$  polynomials of size  $\Theta\left(\sqrt{n}\right)$  while manufacturing principal roots of unity by zero-padding. Formally, we choose an  $n'=2^{\left\lfloor \frac{\log n}{2}\right\rfloor}$  and rewrite  $R[x]/\langle x^n+1\rangle$  as  $\mathcal{R}[x]/\langle x^{n'}-y\rangle$  where  $\mathcal{R}=R[y]/\langle y^{\frac{n}{n'}}+1\rangle$ . Since the x-degree of a product of two polynomials with coefficient ring  $\mathcal{R}$  is bounded by 2n'-2, one can choose a polynomial modulus with x-degree larger than 2n'-2 for efficient computation. We replace the relation  $x^{n'}\sim y$  with  $x^{2n'}\sim 1$  by zero-padding. Since  $y^{\frac{n}{n'}}=-1$  in  $\mathcal{R}$  by definition, y is a principal  $\frac{2n}{n'}$ -th root of unity supporting a size- $\frac{2n}{n'}$  radix-2 cyclic Cooley-Tukey FFT over  $\mathcal{R}$ . By the choice of n',  $\frac{2n}{n'}\geq 2n'$  and  $\mathcal{R}[x]/\langle x^{2n'}-1\rangle$  splits into polynomial rings of the form  $\mathcal{R}[x]/\langle x-y^i\rangle$  with additions, subtractions, and multiplications by powers of y in  $\mathcal{R}$ . Since multiplications by powers of y amount to negacyclic shifts, the entire transformation only requires additions and subtractions in R. If we apply the idea recursively, then the computing task is converted into  $R^h$  where h grows proportionally to  $n\log_2 n$ . In this work, we apply the idea only once and switch to different approaches for the small-dimensional computing task.

# 2.5 Toeplitz Matrix-Vector Product

In lattice-based cryptography, the Toeplitz matrix-vector product (TMVP) was applied to Saber and NTRU on Cortex-M4 [IKPC20, IKPC22], and NTRU and NTRU Prime on Cortex-A72 [Hwa24a, CCHY24]. Conceptually, for an algebra homomorphism multiplying polynomials in R[x], its module-theoretic dual implements a Toeplitz matrix-vector product with the same algebraic complexity [Fid73, Win80, CCHY24]. We call a square matrix Toeplitz if elements belonging to the same diagonal are the same, and a matrix-vector product TMVP if the matrix is a Toeplitz matrix. Prominent examples are polynomial multiplications modulo  $x^n - \zeta$  for a  $\zeta \in R$ . Suppose we have an algebra homomorphism f computing the product  $ab = f^{-1}(f(a)f(b))$  of two size-n polynomials a, b in R[x], then  $f^* \circ (b' \mapsto f(a)b')^* \circ (f^{-1})^*$  (b) computes the reversal of an  $n \times n$  TMVP where  $^*$  is the module-theoretic dualization, corresponding to matrix transposition in terms of matrix manipulation.

**Asymmetric nature of TMVP.** The observation relevant to us is the asymmetric nature of TMVP, which was first introduced under the name "asymmetric multiplication"

in  $[BHK^+22b]^4$ : In practice, the dual of a module homomorphism usually results in the same algebraic complexity. If  $f^{-1}$  is much more expensive than f, dualizing the entire process and applying  $(f^{-1})^*$  to the most frequently used operand is more advantageous. For example, suppose we want to compute polynomial products  $a_0b$  and  $a_1b$  whose reversals are Toeplitz matrix-vector products. If we proceed symmetrically, we need three (fast) f's and two expensive  $f^{-1}$ 's. We can instead dualize the maps and apply  $(f^{-1})^*$  to b. The remaining operations are equivalent to applying four f's, replacing an expensive  $f^{-1}$  by an  $f^*$ .

A running example with Karatsuba. We illustrate the idea with Karatsuba [KO62] shown in [Win80]. Suppose we have an algebra homomorphism computing  $(a_0 + a_1x)(b_0 + b_1x) = a_0b_0 + (a_0b_1 + a_1b_0)x + a_1b_1x^2$  by first applying the forward map  $a_0 + a_1x \mapsto (a_0, a_0 + a_1, a_1)$  to both operands. We then multiply the resulting images and apply the "inversion map"  $(c_0, c_1, c_2) \mapsto c_0 + (c_1 - c_0 - c_2)x + c_2x^2$ . This gives us the desired product  $a_0b_0 + (a_0b_1 + a_1b_0)x + a_1b_1x^2$ . We illustrate how to turn the above computation into a computation implementing the Toeplitz matrix-vector product  $\begin{pmatrix} c_1 & c_2 \\ c_0 & c_1 \end{pmatrix} \begin{pmatrix} a_0 \\ a_1 \end{pmatrix}$ . For the vector, we compute  $(a_0, a_0 + a_1, a_1)$  same as before. As for the Toeplitz matrix, we extract the elements  $c_0, c_1, c_2$  and apply the dual (or transpose in the matrix view) of the "inversion map". This gives us  $(c_0 - c_1, c_1, c_2 - c_1)$ . We then point-multiply them and receive  $((c_0 - c_1)a_0, c_1(a_0 + a_1), (c_2 - c_1)a_1)$ . Finally, we apply the dual of  $(b_0, b_1) \mapsto (b_0, b_0 + b_1, b_1)$  and receive  $(c_0a_0 + c_1a_1, c_1a_0 + c_2a_1)$ , which is the reversal of the desired result.

Naming convention of TMVP. For an algebra homomorphism f multiplying polynomials in R[x], we denote the resulting Toeplitz matrix-vector product as Toeplitz-f. Furthermore, due to the asymmetric nature of TMVP, we denote Hom-V for the module homomorphism applied to the vector operand and Hom-M for the module homomorphism applied to the Toeplitz matrix operand. For the resulting small dimensional TMVP, we denote it as BiHom since it is a bilinear map that is rarely a ring multiplication. Finally, we denote Hom-I for the homomorphism mapping the resulting small dimensional products to the desired result and call it an interpolation.

## 2.6 Dilithium

Dilithium [ABD<sup>+</sup>20a] is a digital signature based on "Fiat-Shamir with aborts" [Lyu09]. The security of Dilithium relies on the Module Small Integer Solutions and the Module Learning with Errors problems. The module is a  $k \times \ell$  matrix over the polynomial ring  $R_q := \mathbb{Z}_q[x]/\langle x^{256}+1\rangle$  where  $q=2^{23}-2^{13}+1$  is a prime and  $(k,\ell)=(4,4),(6,5),(8,7),$  depending on the security level. See Table 1 for an overview of parameter sets.

Table 1: Dilithium parameters [ABD<sup>+</sup>20a] relevant to this work.

| Parameter set | NIST security level | k | $\ell$ | $\eta$ | au | # rep. |

|---------------|---------------------|---|--------|--------|----|--------|

| dilithium2    | II                  | 4 | 4      | 2      | 39 | 4.25   |

| dilithium3    | III                 | 6 | 5      | 4      | 49 | 5.1    |

| dilithium5    | V                   | 8 | 7      | 2      | 60 | 3.85   |

During the key generation, we sample a  $k \times \ell$  matrix  $\hat{A}$  over the image of a negacyclic NTT defined on  $\mathbb{Z}_q[x]/\langle x^n+1\rangle$  and two vectors  $s_1$  and  $s_2$  of polynomials with coefficients drawn from  $\{-\eta,\ldots,0,\ldots,\eta\}$ . We then compute the matrix-vector product  $As_1$  and add  $s_2$  to the result. Finally, we round the result and hash (cf. Algorithm 3). In the signature

<sup>&</sup>lt;sup>4</sup>See [Hwa22, Section 8.3.2] for their relations.

generation, we compute a matrix-vector product where the vector is sampled with a nonce  $(\kappa \text{ in Algorithm 5})$  as one of the parameters. We then compute a challenge polynomial c with exactly  $\tau \pm 1$ 's and  $256 - \tau$  0's from the product and test if it meets the security requirements. During the testing, we compute the vector of products  $cs_1, cs_2$ , and  $ct_0$  where  $s_1$  and  $s_2$  are the same as key generation and  $t_0$  a polynomial with coefficients in  $\{-2^{12}, \ldots, 0, \ldots, 2^{12} - 1\}$  ( $t_0$  is the lower part of the rounding in the key generation). See Algorithm 5 for the details. If any tests fail, we increment the nonce and restart the signature generation. In Table 1, we list the expected number of iterations for generating a desired signature. In the signature verification, we compute a matrix-vector product (cf. Algorithm 4).

This work optimizes the polynomial arithmetic. We outline the target operations of this paper in Algorithms 3-5. Operations in blue are covered by this work and operations in purple are covered by  $[\text{HAZ}^+24]$  and this work. The polynomial arithmetic improvement of  $[\text{HAZ}^+24]$  does *not* apply to the operations in blue in Algorithms 3-5.

```

Algorithm 3 Dilithium key generation. Algorithm 4 Dilithium verification.

Output: sk = (r, K, tr, s_1, s_2, t_0)

Input: pk = (r, t_1), M \in \{0, 1\}^*

Output: pk = (r, t_1)

Input: \sigma = (z, h, \tilde{c})

1: r \leftarrow \{0,1\}^{256}

Output: Valid or Invalid

1: \hat{A} \in R_q^{k \times \ell} \leftarrow \operatorname{ExpandA}(r)

2: K \leftarrow \{0,1\}^{256}

2: \hat{z} \leftarrow \mathsf{NTT}(z)

3: (s_1, s_2) \leftarrow S_{\eta}^{\ell} \times S_{\eta}^{k}

4: \ \hat{A} \in R_q^{k \times \ell} \leftarrow \mathtt{ExpandA}(r) \\ 5: \ \hat{s}_1 \leftarrow \mathsf{NTT}(s_1)

3: \mu \in \{0,1\}^{384} \leftarrow \mathcal{H}(\mathcal{H}(r||t_1)||M)

4: c \leftarrow \mathcal{H}_B(\tilde{c})

5: w_1' \leftarrow \mathsf{NTT}^{-1}\left(\hat{A}\hat{z}\right) - 2^d c t_1

6: t \leftarrow \mathsf{NTT}^{-1}\left(\hat{A}\hat{s}_1\right) + s_2

6: w_1' \leftarrow \mathtt{UseHint}(h, w_1')

7: (t_1, t_0) \leftarrow \text{Power2Round}(t)

8: tr \in \{0,1\}^{256} \leftarrow \mathcal{H}(r||\mathbf{t}_1)

7: if \tilde{c} \neq \mathcal{H}(\mu||w_1') or

8:

||z||_{\infty} \ge \gamma_1 - \beta or

# 1's in h \le \omega then

9:

return Invalid

10:

11: end if

```

#### 2.7 Cortex-M3

Cortex-M3 implements the instruction set architecture Armv7-M and is heavily used in industry, including NXP general purpose microcontrollers<sup>5</sup>, Infineon microcontrollers<sup>6</sup>, and more. We briefly describe the relevant instructions in Armv7-M [ARM21b] and their timing on Cortex-M3 [ARM10a]. add adds up two 32-bit values and sub subtracts them. adc and sbc add and subtract the values with carry. 1s1 and 1sr logically shift a 32-bit value left and right by the specified constant/register value. asr performs an arithmetic right-shift. ubfx extracts certain consecutive bits and unsigned-extends the result to a 32-bit value. sbfx signed-extends the result to a 32-bit value. Each of the above instructions takes one cycle (we exclude the instruction timing involving PC operands). mul multiplies two 32-bit values, mla accumulates the product to the accumulator, and mls subtracts the product from the accumulator. mul takes one cycle and mla/mls takes two cycles. {u, s}mull computes the 64-bit unsigned/signed product of two 32-bit values, and {u, s}mla1 accumulates the product to an accumulator. {u, s}{mul, mla}1 takes 3 to 7 cycles and is input-dependent [ARM10a, Table 18-1]. On Cortex-M4, a close relative of Cortex-M3, all the arithmetic instructions take one cycle. See Table 2 for the instruction timings of

$<sup>^5</sup> https://www.nxp.com/products/processors-and-microcontrollers/arm-microcontrollers/general-purpose-mcus: GENERAL-PURPOSE-MCUS.$

$<sup>^6 {\</sup>tt https://www.infineon.com/cms/en/product/microcontroller/}.$

#### Algorithm 5 Dilithium signature generation.

```

Input: sk = (r, K, tr, s_1, s_2, t_0), M \in \{0, 1\}^*

Output: Signature \sigma = (z, h, \tilde{c})

1: \ \hat{A} \in R_q^{k \times \ell} := \mathtt{ExpandA}(r); \ \mu \in \{0,1\}^{512} \leftarrow \mathcal{H}(tr||M); \ r' \in \{0,1\}^{512} \leftarrow \mathcal{H}(K||\mu); \ \kappa \leftarrow 0

2: \hat{s}_1 \leftarrow \mathsf{NTT}(s_1); \hat{s}_2 \leftarrow \mathsf{NTT}(s_2); \hat{t}_0 \leftarrow \mathsf{NTT}(t_0)

3: (z,h) \leftarrow \bot

4: while (z,h) = \perp do

y \in S^\ell_{\gamma_1-1} \leftarrow \mathtt{ExpandMask}(r',\kappa)

\hat{y} \leftarrow \mathsf{NTT}(y); \ w \leftarrow \mathsf{NTT}^{-1}\left(\hat{A}\hat{y}\right)

6:

\begin{aligned} w_1 &\leftarrow \mathtt{HighBits}(w); \ \tilde{c} \in \{0,1\}^{256} \leftarrow \mathcal{H}(\mu||w_1); \ c \leftarrow \mathcal{H}_B(\tilde{c}) \\ \hat{c} &\leftarrow \mathsf{NTT}(c); \ z \leftarrow y + \mathsf{NTT}^{-1}\left(\hat{c}\hat{s}_1\right); \ r \leftarrow \mathsf{NTT}^{-1}\left(\hat{c}\hat{s}_2\right) \end{aligned}

8:

r_0 \leftarrow \texttt{LowBits}(w-r)

9:

if ||z||_{\infty} \ge \gamma_1 - \beta or ||r_0||_{\infty} \ge \gamma_2 - \beta then

10:

11:

(z,h) = \bot

12.

h \leftarrow \mathsf{NTT}^{-1}\left(\hat{c}\hat{t}_0\right)

13:

h \leftarrow \mathtt{MakeHint}\left(-h, w - r + h\right)

14:

if ||ct_0||_{\infty} \ge \gamma_2 or # 1's in h > \omega then

15:

(z,h) = \bot

16:

end if

17:

18:

end if

19:

\kappa \leftarrow \kappa + 1

20: end while

```

the relevant arithmetic instructions on Cortex-M3 and Cortex-M4.

Constant-time concerns of Cortex-M3 long multiplications. The variable runtime of the long multiplications (smull, smlal, umull, umlal) on Cortex-M3 is a critical issue for computing on secret data. In the literature, [GOPT10] showed that variable-time multiplication instructions led to straightforward timing side-channel attacks. A workaround is to emulate the long multiplications with multi-limb arithmetic [GKS21], resulting in a significant performance penalty.

Table 2: Summary of instruction timings on Cortex-M3 and Cortex-M4 where inputs are 32-bit registers.

| Instruction                               | Cycle     |           |  |

|-------------------------------------------|-----------|-----------|--|

| Histi detion                              | Cortex-M3 | Cortex-M4 |  |

| add/adc/sub/sbc/lsl/lsr/asr/ubfx/sbfx/mul | 1         | 1         |  |

| mla/mls                                   | 2         | 1         |  |

| smull/smlal/umull/umlal                   | 3-7       | 1         |  |

# 3 Algorithm Designs

# 3.1 Modular Multiplications

We first go through our implementations of modular multiplications. Convention-wise, we call a multiplication modular multiplication if it computes a number equivalent to the

product modulo an odd number with the same arithmetic precision. Otherwise, we call it a plain multiplication.

#### 3.1.1 Integer Approximation: Revisited

We generalize the notion of integer approximations. For a function  $[]]: \mathbb{R} \to \mathbb{Z}$ , we call it an integer approximation if  $\exists \delta \in \mathbb{R}_{>0}, \forall r \in \mathbb{R}, |r - [\![r]\!]| \leq \delta$ . When  $\delta$  is known, we call  $[]\![]$  a  $\delta$ -integer-approximation. The generalizations of  $\operatorname{mod}^{\mathbb{I}}$  and  $|\operatorname{mod}^{\mathbb{I}}q|$  are defined in the same way.

#### 3.1.2 Generalizing Barrett Multiplication

Let  $a \in \left[-\frac{\mathtt{R}}{2}, \frac{\mathtt{R}}{2}\right)$ ,  $b \in \left[-\frac{q}{2}, \frac{q}{2}\right)$  be integers. Recall that Barrett multiplication computes a representative of  $ab \bmod q$  as  $ab - \left[\!\left[\frac{a\left[\frac{b\mathtt{R}}{q}\right]_{0}}{\mathtt{R}}\right]_{1}^{q}q$  for integer approximations  $\left[\!\left[\right]_{0}, \left[\right]_{1}^{q}\right]_{1}^{q}$ . If we choose  $\left[\!\left[\right]_{0} = \left[\right]_{1}^{q} = \left[\right]_{1}^{q}\right]_{1}^{q}$ , we have the standard Barrett multiplication. If we choose  $\left[\!\left[\right]_{0} = \left[\right]_{1}^{q}\right]_{1}^{q}$  and  $\left[\!\left[\right]_{1}^{q} = \left[\right]_{1}^{q}\right]_{1}^{q}$ , we compute a representative of  $ab \bmod tq$  with absolute value bounded by 1.75q since the images of  $\left[\!\left[\right]_{1}^{q}\right]_{1}^{q}$  and  $\left[\!\left[\right]_{1}^{q}\right]_{1}^{q}$  and  $\left[\!\left[\right]_{1}^{q}\right]_{1}^{q}$  the floor variant of Barrett multiplication. We show that careful choices of  $\left[\!\left[\right]_{1}^{q}\right]_{1}^{q}$  are of practical importance. We choose  $\left[\!\left[\right]_{0}^{q}\right]_{1}^{q}$  and  $\left[\!\left[\right]_{1}^{q}\right]_{1}^{q}$  the following integer approximation:

$$\forall r \in \mathbb{R}, \llbracket r \rrbracket_b \coloneqq \left| \frac{a_l b_h}{\sqrt{\mathbb{R}}} \right| + \left| \frac{a_h b_l}{\sqrt{\mathbb{R}}} \right| + a_h b_h$$

where  $a_l + a_h \sqrt{R} = \frac{rR}{\left[\!\left[\frac{bR}{q}\right]\!\right]_0}$ ,  $b_l + b_h \sqrt{R} = \left[\!\left[\frac{bR}{q}\right]\!\right]_0$  and  $a_l, b_l \in [0, \sqrt{R})$  and call the resulting Barrett multiplication the approximate variant. We first prove  $|\lfloor r \rceil - [\![r]\!]_b| \leq 3$  as follows. *Proof.*

$$\begin{aligned} & | \lfloor r \rceil - \llbracket r \rrbracket_b | \\ & = & \left| \left\lfloor \frac{\left( a_h b_h + \frac{1}{2} \right) \mathbb{R} + \left( a_l b_h + a_h b_l \right) \sqrt{\mathbb{R}} + a_l b_l}{\mathbb{R}} \right\rfloor - \left( a_h b_h + \left\lfloor \frac{a_l b_h}{\sqrt{\mathbb{R}}} \right\rfloor + \left\lfloor \frac{a_h b_l}{\sqrt{\mathbb{R}}} \right\rfloor \right) \right| \\ & = & \left| \left\lfloor \frac{1}{2} + \left( \frac{a_l b_h}{\sqrt{\mathbb{R}}} - \left\lfloor \frac{a_l b_h}{\sqrt{\mathbb{R}}} \right\rfloor \right) + \left( \frac{a_h b_l}{\sqrt{\mathbb{R}}} - \left\lfloor \frac{a_h b_l}{\sqrt{\mathbb{R}}} \right\rfloor \right) + \frac{a_l b_l}{\mathbb{R}} \right\rfloor \right| \\ & \leq & \left| \left\lfloor \frac{1}{2} + \frac{\sqrt{\mathbb{R}} - 1}{\sqrt{\mathbb{R}}} + \frac{\sqrt{\mathbb{R}} - 1}{\sqrt{\mathbb{R}}} + \frac{\left(\sqrt{\mathbb{R}} - 1\right)^2}{\mathbb{R}} \right\rfloor \right| \\ & = & \left| \left\lfloor \frac{1}{2} + \frac{3\mathbb{R} - 4\sqrt{\mathbb{R}} + 1}{\mathbb{R}} \right\rfloor \right| \\ & = & 3. \end{aligned}$$

Since  $||r| - [r]|_b| \le 3$ , we have

$$\left|ab - \left[ \left[ \frac{a \left[ \left[ \frac{b\mathbf{R}}{q} \right] \right]_0}{\mathbf{R}} \right]_0 \right| \right| \leq \left|ab - \left[ \frac{a \left[ \left[ \frac{b\mathbf{R}}{q} \right] \right]_0}{\mathbf{R}} \right] q \right| + 3q \leq \frac{q}{2} \left( 7 + \frac{|a|}{\mathbf{R}} \right).$$

Therefore, computing with  $ab - \left[\!\left[\frac{a\left[\!\left[\frac{b\mathbb{R}}{q}\right]\!\right]_0}{\mathbb{R}}\right]\!\right]_b q$  is tolerable as long as  $\frac{q}{2}\left(7 + \frac{|a|}{\mathbb{R}}\right) < \frac{\mathbb{R}}{2}$ . In Dilithium, this is the case since  $q < 2^{23}$  and  $\mathbb{R} = 2^{32}$ . The benefit is that  $\left[\!\left[\right]_1$  is faster than

$\lceil \rceil$  if we have to emulate them with  $\frac{\log_2 \mathtt{R}}{2} = \frac{\log_2 \mathtt{R}}{2} \times \frac{\log_2 \mathtt{R}}{2}$  low multiplication instructions<sup>7</sup>. Furthermore, we can also choose  $\lceil \rceil_1 =_b \lceil \rceil$  as follows:

$$\forall r \in \mathbb{R}, b[\![r]\!] := \left| \frac{a_l b_h + \frac{\sqrt{R}}{2}}{\sqrt{R}} \right| + \left| \frac{a_h b_l}{\sqrt{R}} \right| + a_h b_h$$

and find  $|\lfloor r \rceil - b \llbracket r \rrbracket| \le 2$ . We call the resulting Barrett multiplication the half-approximate variant. See Table 3 for an overview of the variants of Barrett multiplication.

Table 3: Overview of the variants of Barrett multiplications. Upper bounds stand for the upper bounds of the absolute values of the results.

| Name             | $\mathbb{I}_0$ | $[]_1$                    | Upper bound                                        | Upper bound when $ a  \leq \frac{R}{2}$ |

|------------------|----------------|---------------------------|----------------------------------------------------|-----------------------------------------|

| Standard         | []             | []                        | $\frac{q}{2}\left(1+\frac{ a }{\mathtt{R}}\right)$ | 0.75q                                   |

| Floor            | []             | IJ                        | $\frac{q}{2}\left(3+\frac{ a }{\mathtt{R}}\right)$ | 1.75q                                   |

| Half-approximate | L7             | b[]]                      | $\frac{q}{2}\left(5+\frac{ a }{R}\right)$          | 2.75q                                   |

| Approximate      | L]             | $\llbracket \rrbracket_b$ | $\frac{q}{2}\left(7+\frac{ a }{\mathtt{R}}\right)$ | 3.75q                                   |

#### 3.2 Transformations

We go through the transformations in this section. Section 3.2.1 goes through the multiplication-based NTT/iNTT and Section 3.2.2 goes through the fast homomorphism modulo  $\mathbb{Z}_{2^k}$ .

#### 3.2.1 Multiplication-Based NTT/iNTT

This paper presents two classes of multiplication-based NTT/iNTT. The first is the NTT and iNTT mandated by Dilithium, which we call Dilithium NTT and iNTT. The second one is the 16-bit NTT/iNTT for the multiplication by the challenge polynomial in the signature generation of Dilithium.

**Dilithium NTT/iNTT.** For the Dilithium NTT/iNTT, since one is asked to compute a certain transformation, there are not many implementation choices. The main focus is on choosing an efficient modular multiplication. We choose Barrett multiplication for the Dilithium NTT/iNTT throughout this paper. Two variants come to our mind – the floor variant avoiding the addition of  $\frac{R}{2}$  and the approximate variant avoiding the computation of the low parts in the high multiplication.

Correctness of the Barrett-based NTT/iNTT. We argue that our Barrett-based NTT/iNTT is correct as there are no overflows throughout the computation. Our argument follows the traditional range analysis. Suppose the result of a modular multiplication has an absolute value bounded by  $\theta q$  for a positive real number  $\theta$ . In Dilithium NTT, since each layer of butterflies increases the absolute values of the coefficients by at most  $\theta q$  and there are eight layers of butterflies, the resulting values have absolute values bounded by  $(8\theta+1) q$ . As long as  $(8\theta+1) q < \frac{\aleph}{2}$ , there are no overflows. This implies that any choices of  $\theta \leq 31.90 < \frac{\frac{\aleph}{2}q-1}{8}$  are sufficient for  $q=2^{23}-2^{13}+1$  and  $\aleph=2^{32}$ . We have  $\theta \leq 0.75$

<sup>&</sup>lt;sup>7</sup>In the reference manual of Armv7-M [ARM21b], multiplication instructions are sometimes denoted as  $w0 = w1 \times w2$  multiplication instructions for several combinations of bit sizes w0 for the output, w1 for the first input, and w2 for the second input. We follow the same convention.

for the standard one,  $\theta \leq 1.75$  for the floor variant,  $\theta \leq 2.75$  for the half-approximate variant, and  $\theta \leq 3.75$  for the approximate variant based on Table 3. Table 4 summarizes the upper bounds of the modulus q for various choices of  $\theta$ 's. Recently, there have been continuous efforts to formally verify the implementation correctness of critical subroutines, including [HLS<sup>+</sup>22] with CryptoLine and [ABB<sup>+</sup>23] with EasyCrypt. In principle, the ideas of [HLS<sup>+</sup>22] and [ABB<sup>+</sup>23] work, but we believe formal verification is out of the scope of this work.

Table 4: Relations between the quality  $\theta$  of a modular multiplication and the modulus q for a 7-layer radix-2 Cooley–Tukey FFT. The approaches of modular multiplication are sorted in the increasing order of the computational efficiency on Cortex-M3.

|              | $\theta$ | Upper bound of $q$ | Upper bound of $\log_2 q$ |

|--------------|----------|--------------------|---------------------------|

| Standard     | 0.75     | 306 783 378        | 28.1926                   |

| Floor        | 1.75     | 143165576          | 27.0931                   |

| Half-approx. | 2.75     | 93 368 854         | 26.4763                   |

| Approximate  | 3.75     | 69 273 666         | 26.0458                   |

**Experimental analysis.** Instead of formal verification, we provide some experimental analyses for the range of the intermediate coefficients throughout the computation of Dilithium NTT with the approximate variant of Barrett multiplication. Table 5 illustrates the upper bounds of the absolute values of the intermediate coefficients layer by layer.

Table 5: Upper bounds of the absolute values of intermediate coefficients throughout an NTT computation with random inputs.

|         | Input      | Output     | Output $(\log_2\text{-scale})$ |

|---------|------------|------------|--------------------------------|

| Layer 0 | 8 363 648  | 27 234 418 | 24.70                          |

| Layer 1 | 27 234 418 | 41 063 339 | 25.30                          |

| Layer 2 | 41 063 339 | 49 941 104 | 25.58                          |

| Layer 3 | 49 941 104 | 61 183 326 | 25.87                          |

| Layer 4 | 61 183 326 | 73057383   | 26.13                          |

| Layer 5 | 73057383   | 75903955   | 26.18                          |

| Layer 6 | 75903955   | 88 663 707 | 26.41                          |

| Layer 7 | 88 663 707 | 93 546 600 | 26.48                          |

Polynomial multiplications with 16-bit arithmetic. Recall that in Dilithium, c is a polynomial with  $\tau \pm 1$ 's and  $256 - \tau$  0's, and  $s_1$  and  $s_2$  are vectors of polynomials with coefficients in  $\{-\eta, \ldots, 0, \ldots, \eta\}$ , the vectors of products  $cs_1$  and  $cs_2$  can be computed over a sufficiently large modulus bounding the maximum possible coefficient in the results [AHKS22]. [AHKS22] applied the idea to Dilithium on Cortex-M4, and showed that Fermat number transform with the coefficient ring  $\mathbb{Z}_{257}$  is the fastest approach for the security levels II and V. For the security level III, since  $\eta$  is too large, they chose  $\mathbb{Z}_{769}$  as the coefficient ring and resorted to standard 16-bit NTT. In prior Cortex-M3 work [HAZ<sup>+</sup>24] exploiting the same idea of small NTT, they argued the benefit of code sharing between multiple parameter sets, while the whole point of their paper is about optimization for speed. We implement FNT on Cortex-M3 with butterflies from [BHK<sup>+</sup>22a] and a refined

variant of [HZZ<sup>+</sup>24, HAZ<sup>+</sup>24]'s Plantard reduction based on [AMOT22] and outperform their small NTT implementation for security levels II and V in speed as we will see in Section 5.2.

#### 3.2.2 The Fast Homomorphism Modulo Powers of Two

This section describes our polynomial multiplier for  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$  with  $k=0,1,\ldots,24$  operating over 32-bit registers. In the signature of Dilithium, we also need to multiply the challenge polynomial c by  $t_0$  whose elements reside in  $\{-2^{12},\ldots,0,\ldots,2^{12}-1\}$ . Following the previous paragraph, one can compute the product  $ct_0$  modulo a q with  $q \geq 491520 \geq 2 \cdot \tau \cdot 2^{12}$ . We compute with the modulus  $q = 2^{19} > 491520$ .

Nussbaumer FFT in theory. Notice that  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$  admits substructures isomorphic to  $\mathbb{Z}_{2^k}[y]/\langle y^{2^{8-h}}+1\rangle$  via  $x^{2^h}\sim y$  for some h's. We introduce the equivalence  $x^{16}\sim y$  (so  $y^{16}\sim -1$ ) and replace it with  $x^{32}\sim 1$ . If we regard the 2-indeterminate polynomial ring as a polynomial ring in x, we find that y is a principal 32-nd root of unity since  $y^{16}=-1$  (cf. Section 2.3). Therefore,  $x^{32}-1$  splits into  $\prod_i (x-y^i)$ . We then apply size-32 cyclic Cooley–Tukey FFT in x with y as the principal 32-nd root of unity.

Nussbaumer FFT in practice. In practice, replacing  $x^{16} \sim y$  by  $x^{32} \sim 1$  amounts to zero padding that is merged with the FFT computation. As for the FFT-based polynomial multiplication, we have to multiply the inverse of the transformation size 32 at the end. Since 32 is not invertible in  $\mathbb{Z}_{2^k}$ , we replace the coefficient ring  $\mathbb{Z}_{2^k}$  by  $\mathbb{Z}_{2^{k+5}}$  for adjoining divisions by  $32^8$ . The resulting polynomial ring is permuted due to Cooley–Tukey FFT. We summarize the transformations so far as follows:

$$\frac{\mathbb{Z}_{2^k}[x]}{\langle x^{256}+1\rangle} \cong \frac{\left(\frac{\mathbb{Z}_{2^k}[y]}{\langle y^{16}+1\rangle}\right)[x]}{\langle x^{16}-y\rangle} \hookrightarrow \frac{\left(\frac{\mathbb{Z}_{2^{k+5}}[y]}{\langle y^{16}+1\rangle}\right)[x]}{\langle x^{32}-1\rangle} \cong \prod_{i_0,...,i_4=0,1} \frac{\left(\frac{\mathbb{Z}_{2^{k+5}}[y]}{\langle y^{16}+1\rangle}\right)[x]}{\left\langle x-y^{\sum_j i_j 2^j}\right\rangle}.$$

Analyzing the number of multiplications. For simplicity, we assume  $n \geq 2$  is a power of two with exponent a power of two. In the literature, a size-n Nussbaumer FFT for  $R[x]/\langle x^n+1\rangle$  requires  $\Theta\left(n\lg n\max\left(\lg\lg n,1\right)\right)$  additions/subtractions and results in  $\frac{n}{2}\lg n$  size-2 polynomials. If we multiply two size-n polynomials with Nussbaumer FFT, we need  $\Theta\left(n\lg n\max\left(\lg\lg n,1\right)\right)$  operations in the coefficient ring. In practice, we need to revise the analysis of the number of multiplications for a concrete analysis. Let's say we recurse until the problem size is smaller than or equal to a platform-dependent power-of-two constant  $t\geq 2$  with exponent a power of two and switch to asymptotically slower approaches, such as the schoolbook, Karatsuba, and Toom-Cook, with  $t^\alpha$  operations where  $1<\alpha<2$  is a constant. The switches to asymptotically slower approaches are typically employed in practice [ACC+21, CHK+21, NG21, ACC+22, BBCT22, AHY22, BHK+22b, BMK+22, Hwa24a]. We revise the number of multiplications in Cooley-Tukey and Nussbaumer FFTs for polynomial multiplications as follows:

• Cooley–Tukey FFT: For the transformation, we need  $\frac{n \lg n}{2 \lg t}$  multiplications for each, and there are three transformations, resulting in  $\frac{3n \lg n}{2 \lg t}$  multiplications. Furthermore, we also have  $\frac{n}{t}$  size-t polynomial multiplications with each requiring  $t^{\alpha}$  multiplications. In total, we need  $\frac{3n \lg n}{2 \lg t} + nt^{\alpha-1}$  multiplications with Cooley–Tukey FFT.

<sup>&</sup>lt;sup>8</sup>By correctness, the last division by 32 is applied to the 32-multiple of the desired result. Replacing  $\mathbb{Z}_{2^k}$  by  $\mathbb{Z}_{2^{k+5}}$  suffices for computing the 32-multiple. This can be justified by the localization of  $\mathbb{Z}$ -algebra [Jac12, Section 7] at non-zero elements.

• Nussbaumer FFT: We don't need multiplications for the transformation, and we have  $\frac{n \lg n}{t \lg t}$  size-t polynomial multiplications with each requiring  $t^{\alpha}$  multiplications. Therefore, we need  $\frac{n t^{\alpha - 1} \lg n}{\lg t}$  multiplications with Nussbaumer FFT.

We compare the factors of the dominating term  $n \lg n$ : we have  $\frac{3}{2 \lg t}$  in Cooley–Tukey and  $\frac{t^{\alpha-1}}{\lg t}$  in Nussbaumer. See Table 6 for a summary. Since t is typically between 4 to 16 by experiments  $[\text{CHK}^+21, \text{BBCT22}]^9$ , Nussbaumer amounts to a much larger number of multiplications. We will later see the numerical justification of our revision in Section 5.2.

Table 6: Overview of the arithmetic cost of Cooley—Tukey and Nussbaumer FFTs for multiplying two size-n polynomials with the threshold t. Transformation cost refers to the number of corresponding arithmetic for transforming the large-dimensional polynomial multiplication into several small-dimensional polynomial multiplications. There are three rows in the transformation cost: (i) the number of additions/subtractions, (ii) the number of multiplications, and (iii) the number of small-dimensional polynomial multiplications after the transformation. Polynomial multiplication cost refers to the number of corresponding arithmetic implementing the large-dimensional polynomial multiplication. We only present the number of multiplications and the dominating term for the polynomial multiplication cost.

|                                | Cooley-Tukey                               | Nussbaumer                                       |  |  |

|--------------------------------|--------------------------------------------|--------------------------------------------------|--|--|

| Transformation cost            |                                            |                                                  |  |  |

| # of add./sub.                 | $\frac{1}{2 \lg t} \cdot n \lg n$          | 0                                                |  |  |

| # of mul.                      | $\frac{1}{\lg t} \cdot n \lg n$            | $\Theta(n \lg n \max(\lg \log_t n, 1))$          |  |  |

| # of small dim. polymul.       | $\frac{n}{t}$                              | $\frac{1}{t \lg t} \cdot n \lg n$                |  |  |

| Polynomial multiplication cost |                                            |                                                  |  |  |

| # of mul.                      | $\frac{3n\lg n}{2\lg t} + nt^{\alpha - 1}$ | $\frac{nt^{\alpha-1}\lg n}{\lg t}$               |  |  |

| Dominating term                | $\frac{3n \lg n}{2 \lg t}$                 | $\frac{\frac{\lg t}{nt^{\alpha-1}\lg n}}{\lg t}$ |  |  |

The remaining computing task are 32 polynomial multiplications in  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$ . We implement it with a Toeplitz matrix-vector product built upon Toom-4.

Toeplitz matrix-vector product from Toom-4 in theory. For simplicity, we describe the Toom-4 [Too63] corresponding to the 4-way split of TMVP used in this work. Suppose we want to multiply two size-4 polynomials  $\sum_{i=0}^{3} a_i x^i$  and  $\sum_{i=0}^{3} b_i x^i$  in R[x]. We apply Toom-4 with the point set  $\{0, \pm 1, \pm 2, \frac{1}{2}, \infty\}$ . This amounts to applying the following

$<sup>^9\</sup>mathrm{One}$  should not confuse the determination of t in polynomial multiplication with the designs of Dilithium and Kyber NTT/iNTT. Kyber [ABD+20b] is a key encapsulation mechanism selected by the NIST Post-Quantum Cryptography Standardization. In Dilithium and Kyber NTTs/iNTTs, the designers chose t=1,2 and mandated one of the operands to be sampled from the transformed domain. Therefore, they are multiplying polynomials in a transformed domain instead of a large-dimensional polynomial ring as in Nussbaumer.

matrix to all the operands with the standard basis  $^{10}$ :

$$\begin{pmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 \\ 1 & 2 & 4 & 8 \\ 1 & -2 & 4 & -8 \\ 8 & 4 & 2 & 1 \\ 0 & 0 & 0 & 1 \end{pmatrix}.$$

After 7 multiplications in R, we apply the following inversion map to the 7-tuple:

$$\begin{pmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 \\ 1 & -1 & 1 & -1 & 1 & -1 & 1 \\ 1 & 2 & 4 & 8 & 16 & 32 & 64 \\ 1 & -2 & 4 & -8 & 16 & -32 & 64 \\ 64 & 32 & 16 & 8 & 4 & 2 & 1 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 \end{pmatrix}^{-1}.$$

This gives us the desired product  $\left(\sum_{i=0}^{3} a_i x^i\right) \left(\sum_{i=0}^{3} b_i x^i\right)$ . The 4-way Toeplitz matrix-vector product used in this work is obtained via a series of dualizations from the module-theoretic point of view. See [CCHY24, Section 4.5] for a constructive correctness proof.

Toeplitz matrix-vector product from Toom-4 in practice. In practice, we need to figure out how to adjoin divisions by powers of two while applying the transformation matrix. Conceptually, we extract all divisions by powers of two, move them to the end of the computation, and implement them with shifts. By the correctness of the Toeplitz matrix-vector product, we will always shift out zeros at the end of the computation. One can show that the requirement of divisions by powers of two is the same as in Toom-4. Since Toom-4 with the point set  $\{0,\pm 1,\pm 2,\frac{1}{2},\infty\}$  requires the divisions by 8, we replace the coefficient ring  $\mathbb{Z}_{2^{k+5}}$  by  $\mathbb{Z}_{2^{k+8}}$ . This explains why our polynomial multiplier only works for  $k=0,1,\ldots,24$  while operating entirely on 32-bit registers.

# 4 Implementations

#### 4.1 Barrett Multiplications

We implement two variants of Barrett multiplications: the first one is the constant-time approximate variant of Barrett multiplication; the second one is the variable-time floor variant of Barrett multiplication. See Table 7 for an overview of the total instruction timings.

Constant-time Barrett multiplication. For the constant-time Barrett multiplication, we compute  $ab - \left[ \frac{a \left\lfloor \frac{2^{32}b}{q} \right\rfloor}{2^{32}} \right]_b^a q$  as a representative of  $ab \mod q$  where  $\left\lfloor \frac{2^{32}b}{q} \right\rfloor$  is precomputed. We first compute  $\left[ \frac{a \left\lfloor \frac{2^{32}b}{q} \right\rfloor}{2^{32}} \right]_b^a$  with Algorithm 6 and then compute the difference of the products ab and  $\left[ \frac{a \left\lfloor \frac{2^{32}b}{q} \right\rfloor}{2^{32}} \right]_b^a q$ . See Algorithm 7 for an illustration. Since our constant-time

$<sup>^{10}</sup>$ The standard basis representing size-n polynomials is  $\left\{1, x, x^2, \dots, x^{n-1}\right\}$ , and the standard basis for a product of polynomial rings is their juxtaposition.

| Table 7: Overview of multiplication operations with 32-bit input values on Cortex-M3. The |

|-------------------------------------------------------------------------------------------|

| cycles are obtained by summing up the instruction timings from the manual [ARM10a].       |

| Plain multiplication                   |           |                 |  |  |  |

|----------------------------------------|-----------|-----------------|--|--|--|

| Multiplication operation               | Work      | Cycle           |  |  |  |

| Long (variable-time)                   | [ARM10a]  | 3-7             |  |  |  |

| Long (constant-time, non-generic)      | [GKS21]   | 11              |  |  |  |

| Long (constant-time)                   | [GKS21]   | 12              |  |  |  |

| Modular multiplication (Constant-Time) |           |                 |  |  |  |

| Montgomery multiplication              | [GKS21]   | 23              |  |  |  |

| Barrett multiplication (approximate)   | This work | 12 (1.92)       |  |  |  |

| Modular multiplication (Variable-Time) |           |                 |  |  |  |

| Montgomery multiplication [GKS21] 9-16 |           |                 |  |  |  |

| Barrett multiplication (floor)         | This work | 6-8 (1.13-2.67) |  |  |  |

Barrett multiplication performs comparably to the constant-time long multiplication, it outperforms any modular multiplication calling a constant-time long multiplication followed by a reduction subroutine with non-negligible cost on Cortex-M3. This explains why our constant-time Barrett multiplication performs 1.92 times faster than the constant-time Montgomery multiplication by [GKS21] with the same input constraints (we assume the inputs are 32-bit numbers since such comparisons are more orthogonal for 32-bit arithmetic whereas [GKS21] assumed the inputs are 16-bit numbers while replacing the memory load operations for words with doubly many load operations for halfwards).

```

Algorithm 6 Implementation of mulhi_split on Cortex-M3.

```

```

Inputs: alo = a_l, ahi = a_h, blo = b_l, bhi = b_h.

Outputs: acchi = a_h b_h + \left\lfloor \frac{a_l b_h}{2^{16}} \right\rfloor + \left\lfloor \frac{a_h b_l}{2^{16}} \right\rfloor.

1: mul acchi,

ahi,

\triangleright acchi = a_h b_h.

\triangleright accmid = a_l b_h.

2: mul accmid.

alo.

bhi

\triangleright acchi = a_h b_h + \left\lfloor \frac{a_l b_h}{2^{16}} \right\rfloor.

3: add acchi, acchi, accmid, asr #16

\triangleright accmid = a_h \vec{b_l}.

4: mul accmid,

ahi,

blo

\triangleright acchi = a_h b_h + \left| \frac{a_l b_h}{2^{16}} \right| + \left| \frac{a_h b_l}{2^{16}} \right|.

acchi, acchi, accmid, asr #16

```

Variable-time Barrett multiplication. For the variable-time Barrett multiplication, we compute  $ab - \left\lfloor \frac{a \left\lfloor \frac{2^{32}b}{q} \right\rfloor}{2^{32}} \right\rfloor q$  as shown in Algorithm 8. Compared to the assembly-optimized variable-time Montgomery multiplication as shown in Algorithm 9, Barrett multiplication turns the smlal into an mls. Since smlal takes 5 to 8 cycles and mls takes only two cycles, Barrett multiplication is obviously faster. Overall, our variable-time Barrett multiplication is 1.13-2.67 times faster than the variable-time Montgomery multiplication by [GKS21].

# 4.2 Dilithium NTT/iNTT

We apply our generalized Barrett multiplication to Dilithium NTT/iNTT. Such NTT/iNTT are required in the matrix-vector multiplication and are not covered by  $[HAZ^+24]$ . To be specific, Lines 5 and 6 in Algorithm 3, Lines 2 and 5 in Algorithm 4, and Line 6 in Algorithm 5.

#### **Algorithm 7** Constant-time Barrett multiplication with 32-bit inputs on Cortex-M3.

#### Algorithm 8 Variable-time Barrett multiplication on Cortex-M3.

Inputs:

$$a = a, b = b, bhi = \left\lfloor \frac{2^{32}b}{q} \right\rfloor$$

.

Outputs:  $c = ab - \left\lfloor \frac{a \left\lfloor \frac{2^{32}b}{q} \right\rfloor}{2^{32}} \right\rfloor q$ .

1: smull lo, hi, a, bhi

2: mul c, a, b

$c = ab \mod \pm 2^{32}$ .

3: mls c, hi, q, c

$c = ab \mod \pm 2^{32}$ .

$c = ab \mod \pm 2^{32}$ .

Choices of Barrett multiplications for constant/variable-time NTT/iNTT. For the matrix-vector multiplications of Dilithium, one should apply constant-time computation to the ones in key generation and signature generation. As for the matrix-vector multiplication in the signature verification, one can compute it with the fastest approach without any side-channel worrisome since verification is public under the context of digital signature. On Cortex-M3, we compute the matrix-vector multiplications in key generation and signature generation with constant-time NTT/iNTT based on the approximate variant of Barrett multiplication and the one in the signature verification with the fastest approach – variable-time NTT/iNTT based on the floor variant of Barrett multiplication. See Table 8 for a summary of the constant-time requirement and the chosen modular multiplications in the NTTs/iNTTs of the matrix-vector multiplications.

Table 8: Constant-time requirements and modular multiplications in the NTTs/iNTTs of matrix-vector multiplications of key generation, signature generation, and signature verification.

|                        | Constant-timeness requir. | Approach (Cortex-M3)          |

|------------------------|---------------------------|-------------------------------|

| Key generation         | ✓                         | Constant-time approx. Barrett |

| Signature generation   | ✓                         | Constant-time approx. Barrett |

| Signature verification | ×                         | Variable-time floor Barrett   |

**Algorithm 9** Variable-time Montgomery multiplication on Cortex-M3 [GKS21, ACC<sup>+</sup>21]. [GKS21] and [ACC<sup>+</sup>21] independently proposed the same computation. [GKS21] applied the idea to Cortex-M3 and Cortex-M4 and [ACC<sup>+</sup>21] applied the idea to Cortex-M4.

```

Inputs: a = a, b = b.

Outputs: hi = \frac{ab + \left(-abq^{-1} \bmod {}^{\pm}2^{32}\right)q}{2^{32}}.

1: smull lo, hi, a, b

2: mul lo, lo, -q^{-1} \bmod {}^{\pm}2^{32}

3: smlal lo, hi, lo, q

\Rightarrow hi = \frac{ab + \left(-abq^{-1} \bmod {}^{\pm}2^{32}\right)q}{2^{32}}.

```

Analyzing the register pressure of layer-merging. Layer-merging is a common memory optimization strategy for software implementations. Conceptually, we load a series of coefficients defining multiple layers of isomorphisms, compute the isomorphisms, and store the results in memory. For the radix-2 NTT/iNTT, the goal is to compute l layers of radix-2 butterflies. We formally analyze the register pressure enabling an l-layer merging for the constant-time and variable-time NTT/iNTT. For an l-layer merge in an NTT/iNTT, we must load  $2^l$  coefficients and  $2^l-1$  twiddle factors. For the variable-time radix-2 NTT/iNTT, since we need  $2^l$  registers for the coefficients and  $2^l-1$  registers for the twiddle factors, we can merge up to two layers. On the other hand, we need  $2^l$  registers for the coefficients and  $3(2^l-1)$  registers for the twiddle factors in our constant-time radix-2 NTT. Therefore, there is no layer-merging in our constant-time radix-2 NTT. As for the iNTT, we apply a similar layer-merging technique from [ACC+22] by observing that some twiddle factors are 1's.

# 4.3 Fast Homomorphism Modulo Powers of Two

For our fast homomorphism for  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$ , we briefly outline the implementation challenges for the Nussbaumer implementing  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle \hookrightarrow \mathcal{R}'[x]/\langle x^{32}-1\rangle \cong (\mathcal{R}')^{32}$  where  $\mathcal{R}'=\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$ . As for the TMVP for  $\mathcal{R}'$ , we find it straightforward for implementation, so we skip the description.

Layer merging in Nussbaumer. Recall that in Nussbaumer, twiddle factor multiplications are negacyclic shifts, and when we move to the next layer, there are doubly many negacyclic shifts where two registers are involved in each butterfly. This implies a factor of 4 blow-up, and we need  $2^{2l-1}$  registers for an l-layer merge. Therefore, we can only merge at most two layers on Cortex-M3.

Optimizing the layer merging during pre- and post-processing in Nussbaumer. We further implement the following optimizations to reduce the memory access during the replacement of  $x^{16} \sim y$  by  $x^{32} \sim 1$ . We skip the explicit replacement of relations and the initial butterflies, and modify the memory load in the follow-up butterflies accordingly. For the converse replacement (replacing  $x^{32} \sim 1$  by  $x^{16} \sim y$ ), we also merge it with the last series of butterflies.

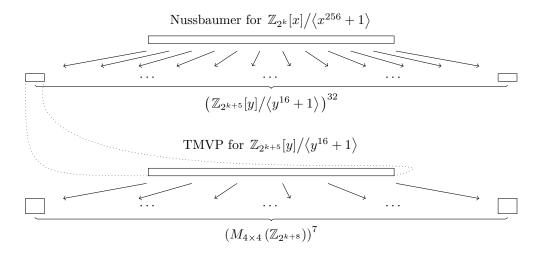

**Memory consumption.** Finally, we outline the memory consumption of the fast homomorphism modulo powers of two. In the beginning, we map each polynomial in  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$  to 32 polynomials in  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$  with Nussbaumer. For each polynomial in  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$ , we map it to seven  $4\times 4$  Toeplitz matrices over  $\mathbb{Z}_{2^{k+8}}$  for one of the operands and seven size-4 vectors over  $\mathbb{Z}_{2^{k+8}}$  for the other operand. For each Toeplitz matrix, we only need to store the first row and the first column, but we allocate 8 words for smooth engineering [IKPC20]. We need  $4\cdot 8\cdot 7\cdot 32=7168$  bytes for

Figure 2: Overview of our fast homomorphism modulo powers of two. There are two phases: (i) Nussbaumer for  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$  and (ii) TMVP for  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$ . Nussbaumer maps  $\mathbb{Z}_{2^k}[x]/\langle x^{256}+1\rangle$  to  $(\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle)^{32}$ . As for TMVP for  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$ , we illustrate the matrix part – each polynomial in  $\mathbb{Z}_{2^{k+5}}[y]/\langle y^{16}+1\rangle$  is expanded into seven  $4\times 4$  Toeplitz matrices. For a Toeplitz matrix, we only store the first row and column explicitly [IKPC20].

the Toeplitz part and  $4\cdot 4\cdot 7\cdot 32=3584$  bytes for the vector part. See Figure 2 for an illustration for the Toeplitz part. In addition, we also need two buffers of 512 words each for the Nussbaumer while saving memory operations with out-of-place computation. In total, we need  $7168+3584+4\cdot 512\cdot 2=14848$  bytes of memory where the buffers for Nussbaumer are shared while multiplying two polynomials with our fast homomorphism modulo powers of two.

## 5 Results

#### 5.1 Benchmarking Environment

We benchmark our Armv7-M implementations on a nucleo-f207zg board containing a stm32f207zg core with 128 KiB of SRAM and 1 MB of flash memory. According to [STM20, Sections 3.2 and 3.6], stm32f207zg provides access to SRAM and flash memory with 0 wait state up to the frequency 120 MHz. Nevertheless, we follow the literature [ACC<sup>+</sup>22] and benchmark at a frequency 30 MHz for consistency. We compile our code with the cross-compiler arm-none-eabi-gcc version 10.3.1. For fair comparisons, we plug in the improved Keccak permutation by [HAZ<sup>+</sup>24] and re-bench the implementations from the literature with this new Keccak permutation.

# 5.2 Performance of Polynomial Multiplications

#### 5.2.1 Dilithium NTT/iNTT

For the Dilithium NTT/iNTT, our constant-time Barrett-based NTT and iNTT are  $1.51\times$  and  $1.38\times$  faster than prior art with constant-time Montgomery multiplications, and our variable-time Barrett-based NTT and iNTT are  $1.21\times$  and  $1.10\times$  faster than prior art with variable-time Montgomery multiplications. See Table 9 for a summary.

|      | Cons    | tant-time     | Varia   | able-time     |

|------|---------|---------------|---------|---------------|

|      | [GKS21] | This work     | [GKS21] | This work     |

| NTT  | 33 025  | 21 876 (1.51) | 19 347  | 15 985 (1.21) |

| iNTT | 36 609  | 26 524 (1.38) | 21 006  | 19067 (1 10)  |

Table 9: Performance numbers of Dilithium NTT/iNTT on Cortex-M3.

#### 5.2.2 Polynomial Multiplications with 16-bit Arithmetic Precision

For the 16-bit arithmetic, our NTT, base multiplication, and iNTT are  $1.08 \times$ ,  $1.41 \times$ ,  $1.11 \times$  faster than prior art by [HAZ<sup>+</sup>24] with no surprises. See Table 10 for a summary.

Table 10: Performance cycles of polynomial multiplications with 16-bit arithmetic precision on Cortex-M3. The numbers of [ACC<sup>+</sup>22] in this table were reported in one of the authors' master thesis [Hwa22, Table 9.10]

| Work             | $[ACC^+22]$         | $[\mathrm{HAZ}^{+}24]$ | This work          |

|------------------|---------------------|------------------------|--------------------|

| Coefficient ring | $\mathbb{Z}_{3329}$ | $\mathbb{Z}_{769}$     | $\mathbb{Z}_{257}$ |

| Approach         | Montgomery          | Plantard               | FNT                |

| NTT              | 8 688 (0.90)        | 7830                   | 7 252 (1.08)       |

| Mul.             | 5 987 (0.67)        | 3 989                  | 2835 (1.41)        |

| iNTT             | 9 553 (0.89)        | 8 543                  | 7667 (1.11)        |

#### 5.2.3 Polynomial Multiplications with 32-bit Arithmetic Precision

For polynomial multiplications with 32-bit arithmetic precision, our polynomial multiplier built upon Nussbaumer FFT and TMVP from Toom-4 is more performant than existing works. We have roughly 1.9 times faster module homomorphism for one of the operands and the interpolation at the expense of slightly slower module homomorphism for the other operand and a slower bilinear map compared to [HAZ<sup>+</sup>24]. See Table 11 for a summary. We demonstrate the impact of the choices of coefficient rings with numerical evidence from the literature [BBCT22, Hwa24a, HAZ<sup>+</sup>24] and this work as follows.

Nussbaumer modulo  $\mathbb{Z}_q$  for an odd q. Section 3.2.2 explains that Nussbaumer intrinsically requires much more multiplications not reflected in the asymptotic analysis of the runtime than Cooley–Tukey. We compare the Schönhage<sup>11</sup>+Nussbaumer approach by [BBCT22] to the multiplication-based NTT approach by [Hwa24a] for multiplying polynomials in  $\mathbb{Z}_{4591}[x]/\langle x^{761}-x-1\rangle$  of NTRU Prime [BBC<sup>+</sup>20]. Both approaches are quite complicated, so we skip the descriptions and focus on the number of small-dimensional polynomial multiplications after the transformations. Both approaches amount to size-8 polynomial multiplications over  $\mathbb{Z}_{4591}$  and are implemented with AVX2 on Haswell processors with the modular multiplication by [Sei18]. The Schönhage+Nussbaumer by [BBCT22] results in 768 size-8 polynomial multiplications, and the multiplication-based NTT by [Hwa24a] results in 192 size-8 polynomial multiplications. Since each modular multiplication in  $\mathbb{Z}_{4591}$  amounts to 3 times the cycles compared to the plain multiplication for the most critical pipeline on Haswell, we would expect a large performance penalty while extending the polynomial rings with Nussbaumer and Schönhage. In fact, the cycles

<sup>&</sup>lt;sup>11</sup>Schönhage [Sch77] is a similar approach crafting the roots of unity.

Table 11: Performance cycles of polynomial multiplications with 32-bit arithmetic precision on Cortex-M3. The total cycles of polynomial multiplications are obtained by summing up all the rows in the building block, and other rows are obtained by benchmarking.

| Work                                  | $[ACC^+22]$                      | $[\mathrm{HAZ}^{+}24]$           | This work                  |

|---------------------------------------|----------------------------------|----------------------------------|----------------------------|

| Coefficient ring                      | $\prod_{i=0,1} \mathbb{Z}_{q_i}$ | $\prod_{i=0,1} \mathbb{Z}_{q_i}$ | $\mathbb{Z}_{2^{\leq 24}}$ |

| Approach                              | Montgomery                       | Plantard                         | Nussbaumer                 |

| Build                                 | ing block                        |                                  |                            |

| NTT/Hom-M                             | 16 774 (0.93)                    | 15626                            | 15 820 (0.99)              |

| NTT/Hom-V                             | 16 774 (0.93)                    | 15626                            | 8 259 (1.89)               |

| Mul./BiHom                            | 11 933 (0.68)                    | 8 061                            | 11 217 (0.72)              |

| iNTT/Hom-I                            | 23 721 (0.88)                    | 20 772                           | 10 960 (1.90)              |

| Polynomial                            | multiplication                   |                                  |                            |

| Total cycles                          | 69 202 (0.87)                    | 60 085                           | 46 256 (1.30)              |

| Ratio of mul./BiHom over total cycles | 17.24%                           | 13.42%                           | 24.25%                     |

| Memory (bytes)                        | 1 536                            | 2 048*                           | 14 848                     |

<sup>\*</sup> In  $[HAZ^+24, Section 4.2.3]$ , the authors claimed to achieve an improvement of stack usage to one-third of Algorithm 5 in  $[ACC^+22]$ . Their statement is invalid. Firstly, Algorithm 5 of  $[ACC^+22]$  computes the masked product with 48-bit precision, and a scientifically valid way is to compare to Algorithm 4 of  $[ACC^+22]$ , which computes the unmasked product with 32-bit precision, the computation what  $[HAZ^+24, Section 4.2.3]$  refers to. Secondly, they claimed that 1024 bytes are used by the polynomial multiplication by sharing the memory usage of one of the operands with something else and removing its memory attribution, whereas  $[ACC^+22]$  reported memory usage with all the operands included and also reused the memory for something else in the implementation. We follow  $[ACC^+22]$ 's comparison methodology.

of the small-dimensional polynomial multiplications in the Schönhage+Nussbaumer FFT approach by [BBCT22] takes 55.24% of the polynomial multiplication cycles, whereas the cycles of the small-dimensional polynomial multiplications in the multiplication-based NTT approach by [Hwa24a] takes only 23.98% of the polynomial multiplication cycles, and the majority of the improvement cycles of [Hwa24a] over [BBCT22] comes from the reduction of small-dimensional polynomial multiplications. In summary, when multiplications in the coefficient ring are slow, Nussbaumer FFT is not a good choice.

Nussbaumer modulo  $\mathbb{Z}_{2^k}$ . Things become quite different when the coefficient ring takes the form  $\mathbb{Z}_{2^k}$ . For the Nussbaumer approach, the small-dimensional polynomial multiplication takes only 24.25% of the overall polynomial multiplication. As for the multiplication-based NTT approach, since the  $\mathbb{Z}_{2^k}$  does not straightforwardly support an NTT, one has to resort to the multi-moduli approach based on the residue number system when there is no efficient 32-bit modular multiplication, such as Cortex-M3 [ACC<sup>+</sup>22, HAZ<sup>+</sup>24] and AVX2 [CHK<sup>+</sup>21]. See Table 12 for a summary of the performance impact of the choices of coefficient rings in Nussbaumer.

Notes on the engineering effort. For the engineering effort of the Nussbaumer and Toeplitz-TC over  $\mathbb{Z}_{2^k}$ , we developed the assembly programs with the aid of the artifact in C associated to [Hwa24b]. According to our development log, only six days were spent from parameter selection to hand-written assembly-optimized implementation without any scripting support. We later developed the C programs for the transformations to facilitate future development. Please find the C programs in the artifact.

Table 12: Summary of the performance impact of the choices of coefficient rings in Nussbaumer and similar approaches versus other approaches. We extracted the small-dimensional polynomial multiplications in the AVX2 programs by [BBCT22, Hwa24a] and benchmarked with the same setting of [Hwa24a] on the same Haswell processor after contacting the author of [Hwa24a].

|                                                                                               | Mul./BiHom         | Total      | Mul./BiHom over Total |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------------|------------|-----------------------|--|--|--|

| Polymul. in $\mathbb{Z}_{4591}/\langle x^{761}-x-1\rangle$ of NTRU Prime with AVX2 on Haswell |                    |            |                       |  |  |  |

| Schönhage/Nussbaumer,<br>[BBCT22]                                                             | 12 960             | 23 460     | 55.24%                |  |  |  |

| Mulbased, [Hwa24a]                                                                            | 2958               | 12336      | 23.98%                |  |  |  |