# Advances in Logic Locking: Past, Present, and Prospects

# Hadi Mardani Kamali, Kimia Zamiri Azar, Farimah Farahmandi, and Mark Tehranipoor

Abstract—Logic locking is a design concealment mechanism for protecting the IPs integrated into modern System-on-Chip (SoC) architectures from a wide range of hardware security threats at the IC manufacturing supply chain. Logic locking primarily helps the designer to protect the IPs against reverse engineering, IP piracy, overproduction, and unauthorized activation. For more than a decade, the research studies that carried out on this paradigm has been immense, in which the applicability, feasibility, and efficacy of the logic locking have been investigated, including metrics to assess the efficacy, impact of locking in different levels of abstraction, threat model definition, resiliency against physical attacks, tampering, and the application of machine learning. However, the security and strength of existing logic locking techniques have been constantly questioned by sophisticated logical and physical attacks that evolve in sophistication at the same rate as logic locking, in this survey paper, we categorize the existing defenses and attacks to capture the most benefit from the logic locking techniques for IP protection, and illuminating the need for and giving direction to future research studies in this topic. This survey paper serves as a guide to quickly navigate and identify the state-of-the-art that should be considered and investigated for further studies on logic locking techniques, helping IP vendors, SoC designers, and researchers to be informed of the principles, fundamentals, and properties of logic locking.

Index Terms—IP Piracy, IC Supply Chain, IP Protection, Logic Locking.

# **1** INTRODUCTION

M ODERN integrated circuit (IC) supply chain has evolved dramatically in the last two decades for multiple reasons, such as ever-increasing cost/complexity of IC manufacturing, huge recurring cost of IC fab maintenance and troubleshooting, aggressive time-to-market, the expedition of the IC supply chain flow, involvement of multiple third-party Intellectual Property (IP) vendors, engagement of cutting-edge technologies, being a primary forerunner in the semiconductor market, etc. [1]. Over time, the economy of scale has pushed for ever-increasing adoption of the IC supply chain's horizontal model. In the IC supply chain's horizontal model, separate entities fulfill various stages of design, fabrication, testing, packaging, and integration of ICs, forming a globally distributed chain.

Plunged in the globalization ocean of the IC supply chain, given the complexity of originally implementing major components of a chip, the design team will bring and acquire multiple  $3^{rd}$  party IPs from numerous IP owners to reduce time-to-market. Additionally, given the overall cost of fabrication, wafer sort, dicing, packaging, package test, and getting access to state-of-the-art technologies, performing most, if not all, these steps in the offshore facility may be the preferred approach for design houses. Outsourcing and the involvement of numerous stakeholders in various stages of the supply chain dramatically reduce the cost and time-to-market of the chip.

Retaining of being competitive is even getting worse especially in the current post-pandemic market, where chip demand is exceeding foundry fab capacity, causing tremendous shortages in the market, which even results in increasing the share prices of major contract chipmakers, including TSMC, UMC, and SMIC [2]. In such a market with this unprecedented demand, we will face a more panic IC design, implementation, manufacturing, and testing by original equipment manufacturers (OEM), which is done precariously to steal the market/contracts. So, with fewer precautions taken by the OEMs to meet the market demand, and by getting more globalization, OEMs and/or IP vendors face a drastic reduction of the control and monitoring capability over the supply chain.

Despite the benefit achieved by the globalization of the IC supply chain, after the involvement of multiple entities within the IC supply chain with no reciprocal trust and lack of reliable monitoring, the control of original manufacturers and IP owners/vendors over the supply chain will be reduced drastically, resulting in numerous hardware security threats, including but not limited to IP piracy, IC overproduction, and counterfeiting [3], [4].

To address threats associated with the horizontal IC supply chains, a variety of design-for-trust countermeasures have been investigated in the literature. Watermarking, IC metering, IC camouflaging, and hardware obfuscation are examples of passive to active design-for-trust countermeasures [5], [6], [7], [8]. In comparison to other Design-for-trust countermeasures, logic locking as a proactive technique for IP protection has garnered remarkable attention in recent years, culminating in a plethora of research over the last two decades on designing a variety of robust solutions at different levels of abstraction.

Logic locking enables the IP/IC designers to provide limited post-fabrication programmability to the fabricated designs, thereby concealing the underlying functionality

K.Z. Azar, H.M. Kamali, F. Farahmandi, M. Tehranipoor are with the Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL, 32611.

E-mail Addresses: h.mardanikamali@ufl.edu, k.zamiriazar@ufl.edu,

*E-mail* Addresses: h.mardanikamali@ufl.edu, k.zamiriazar@ufl.edu, farimah@ece.ufl.edu, tehranipoor@ufl.edu.

behind an ocean of options. The resultant locked circuit functionality is governed by the logic locking secret, known as the key, which is known only to authorized/trusted entities, such as IP owners or original component manufacturers (OCM), and by loading the correct key value, the design house can unlock the circuit. The concept of locking a circuit against malicious or unauthorized activities was first introduced in Lock and Key technique [8], [9], [10]. In this technique, a key-based mechanism has been introduced that add programmability (randomness) to the design-for-testability (DFT) sub-circuits (subchains) when being accessed by an unauthorized user. Over time, this programmability has been extended to other parts of the design, like combinational parts [11], [12], sequential (non-DFT) parts [13], [14], and even parametric/behavioral (non-Boolean) aspects of the design [15]. With high applicability and adaptability of logic locking, a wide range of logic locking techniques currently being explored in both the academic context and semiconductor industries, such as Mentor Graphic's TrustChain platform enabled by logic locking and the newest Defense Advanced Research Projects Agency (DARPA) project on Automatic Implementation of Secure Silicon (AISS) [16], [17].

Logic locking countermeasures appeared as a promising protection mechanism against IP piracy and IC overproduction. However, the development of attacks on logic locking by white hatter researchers, known as logic de-obfuscation attacks, is also essential for the evolution of the logic locking paradigm. This helps the researchers to distinguish between weak and robust countermeasures, highlighting the weaknesses of existing countermeasures and illuminating the need for and giving direction to future research in this area. Hence, for more than a decade, numerous studies investigated logic locking in both defense and attack perspectives. It results in the evolution of both the attacks and countermeasures to become increasingly sophisticated. Furthermore, over time, the emergence of cutting-edge technologies, e.g. failure analysis (FA) equipment [18], [19], [20], application of state-of-the-art approaches like the usage of machine learning [21], [22], and deeper infiltration by the adversaries even into trusted facilities [23], show that the logic locking countermeasures are not yet as mature as what promised from the theoretical point of view.

In this survey paper, we first holistically review the direction of logic locking through the last decade, in both the attack and defense sides. We will define the parameters, characteristics, and assumptions, either directly or indirectly

affect the outcome of logic locking or the de-obfuscation attacks. Then, we will categorize all defenses and attacks and will evaluate each category based on all pre-defined characteristics and parameters, separately. By providing a very comprehensive comparison between different categories, in both the attack and defense sides, this paper helps to delineate the future of logic locking and new possible directions.

The paper is organized as follows. In Section 2, we first provide all background knowledge, including pivotal parameters, characterization, models, and assumptions on logic locking helping us to have a better understanding of the categorization provided through the paper. Then Section 3 provides the details of state-of-the-art logic locking techniques, different breeds, characteristics, etc. Section 4 will also cover all notable de-obfuscation attacks introduced so far on logic locking. Then in Section 5, based on all observations and details covered in this survey, we will discuss the possible futuristic trends in this domain, and finally, Section 6 concludes the paper.

# 2 BACKGROUND: PARAMETERS, MODELS, AND ASSUMPTIONS IN LOGIC LOCKING

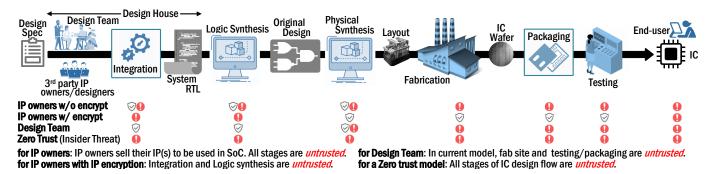

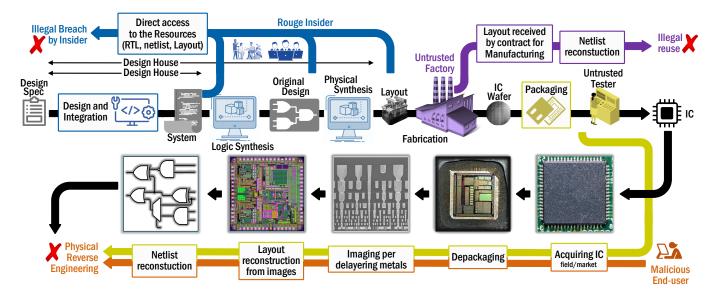

Fig. 1 demonstrates the main steps of modern IC design flow, in which by starting from the design specification, multiple parties will be involved horizontally in the process of IC manufacturing [24], and by outsourcing that can be engaged at different stages, the OEMs have the least reliable form of control to their belongings (the circuitry or the IP), which results in introducing these contracted and mainly offshore entities as the untrusted parties. As for malicious/untrusted entities, from each IC manufacturing stage, per Fig. 2, given any representation of the IC, including integrated design, physically-synthesized netlist, layout, packaged IC, or IC under test, the functionality can be reverse-engineered. The toughest yet possible form of circuit reconstruction is usually referred to as physical reverse-engineering, which can be done by malicious endusers. Successful reverse-engineering, in any form, allows the malicious (untrusted) entities to steal the IP/design and/or illegally over-produce or re-use it.

Given such circumstances, in which the IP vendors or design teams have to protect their belongings (IP and the design (integrated)) against any form of reverse-engineering demonstrated in Fig. 2, we are witnessing different broad categories of design-for-trust techniques, which mainly are

Fig. 1: Conventional (Globalized) IC Design Flow and its Trustworthiness Issue.

FUTURE HARDWARE SECURITY RESEARCH SERIES

Fig. 2: Different Threat Models at Different Stages of IC Design Flow.

(i) IC camouflaging [7], [25], [26], [27], [28], (ii) split manufacturing [29], [30], [31], [32], and (iii) logic locking [10], [11], [12], [33], [34]. Considering the possibility of having reverse-engineering at different layers (as demonstrated in Fig. 2), both IC camouflaging and split manufacturing are applicable to a subset of these threats. For instance, IC camouflaging use high-structural similar logic gates (or other physical structures such as dummy vias) with different functions. However, it is only effective against postmanufacturing attempt(s) of reverse engineering (by the malicious end-user), and it provides no limitations against a foundry's attempt at reverse engineering, as a foundry has access to all masking layers and is not trapped by structural ambiguity for being able to logically extract a netlist. Split manufacturing, on the other hand, is the integration of the transistors and lower metal layers (a.k.a. Front End Of Line (FEOL) layers) fabricated in cutting-edge technology nodes by an untrusted (and mostly offshore) high-end foundry, with higher metal layers (a.k.a. Back End Of Line (BEOL) layers) fabricated at the design house's trusted low-end foundry. This countermeasure alleviates the security risks at the untrusted foundry. However, this methodology still cannot protect the design against malicious end-users and malicious insiders that threaten the confidentiality of the proprietary technology. On the contrary, logic locking -if implemented meticulously- can be a proactive hardwarefor-trust technique that can protect against all previously mentioned threats through the IC supply chain.

# 2.1 Basic Definitions of Logic Locking

Logic locking<sup>1</sup> is the capability of adding post-fabrication programmability that could be added using some extra gates, known as key-programmable gates (key gates) that are driven from the secret of logic locking, i.e. the key. Logic locking techniques could be implemented at different levels

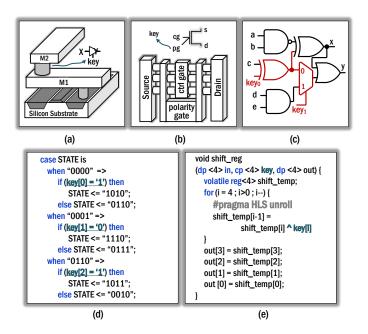

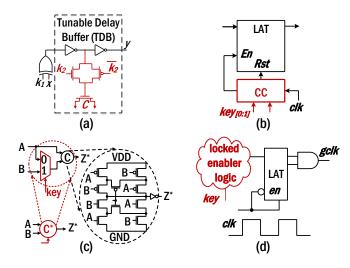

**Fig. 3:** Logic Locking Examples at Different Levels of Abstraction: (a) Layout-level Key-based Routing, (b) Transistor-level Key-based Basic Gates, (c) Key-based Logic/Routing Gate-level, (d) RTL-level Key-based FSM, (e) HLS-level Key-based Shift Register.

of abstraction. Fig. 3 demonstrates a simple example of logic locking in different levels of abstraction. For instance, at layout-level as shown in Fig. 3(a), the metal-insulatormetal (MIM) structure, which connects two adjacent metal layers, has been engaged as key-based programmable unit for routing-based locking [35]. Table 1 shows general specification of logic locking at different layers of abstraction. In general, moving from layout-level to RTL- or HLS-level mitigates the implementation effort. However, at a lower level of abstraction, finding a logic locking countermeasure at lower overhead is easier to be achieved. Furthermore, moving to a higher level of abstraction (like RTL and HLS) can also provide some form of protection against a sub-

<sup>1.</sup> Although the term *logic locking* indicates a specific (gate-level) variation of *hardware obfuscation*, both terms have been widely used interchangeably in the literature. In this paper, we also used *logic locking* as the synonymous word for *hardware obfuscation*.

#### FUTURE HARDWARE SECURITY RESEARCH SERIES

TABLE 1: Logic Locking Specification at Different Abstraction Layers.

| Circuit          | Granularity                      | Overhead | Implementation<br>Effort |

|------------------|----------------------------------|----------|--------------------------|

| Layout-level     | bitwise, wiring                  |          | High                     |

| Transistor-level | bitwise, switching, wiring       |          | High                     |

| Gate-level       | bitwise, logical                 |          | Medium                   |

| RTL-level        | bitwise, operational, behavioral |          | low                      |

| High-level (HLS) | bitwise, operational, behavioral |          | low                      |

set of insider threats. Although at the moment, more than 90% of existing logic locking techniques are introduced and implemented at the gate-level, mostly done as a post-synthesis stage on the synthesized gate-level netlist in the supply chain, we will demonstrate RTL/HLS-based logic locking is one of the pivotal and widely-used current trends in logic locking.

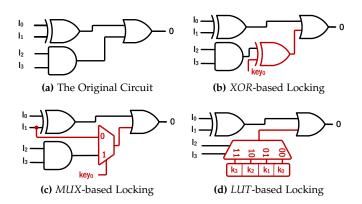

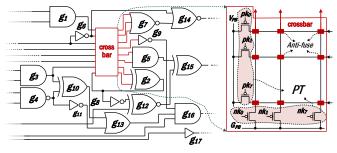

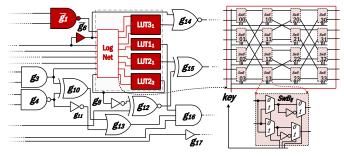

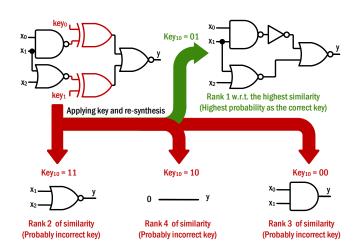

As bitwise form of logic locking is achievable at any abstraction layer, based on the type of key gates, either used for logic locking or obtained after synthesis/compilation, we also can categorize logic locking into three main groups: (1) XOR-based, (2) MUX-based, and (3) LUT-based. As their names imply, they are using eXclusive-OR<sup>2</sup>, MUltipleXers, Look-Up-Tables for obfuscation, respectively. Fig. 4 depicts a simple example of each of these models, demonstrated at gate-level abstraction. It is worth mentioning that except layout-level and transistor-level locking that can be applied for concealment of wiring or switching, for both RTL-level and HLS-level that can target operational or behavioral, the locking part in the resultant netlist generated after synthesis has been implemented using one (or a combination) of these three key-gates. During the last decade, different logic locking techniques commonly have engaged these gates with different structures/functions for locking purposes. Based on some properties of these key gates, such as location, structure, count, intercorrelation, etc., the countermeasures provide various levels of robustness against the existing deobfuscation attacks.

A crucial property of logic locking techniques is the **output corruptibility**. Output corruptibility is a very efficient measure of hiding the design's functionality while the logic locking is in place. Corruptibility means that when an incorrect key is applied to the locked circuit, (1) for

2. For simplicity, we describe it as XOR-based. It can be trivially extended to be XNOR-based as well.

**Fig. 4:** Basic Gates used for Logic Locking, (a) Original, (b) correct key  $(k_0 = 0)$ , (c) correct key  $(k_0 = 1)$ , (d) correct key  $(k_{0:3} = 0001)$ .

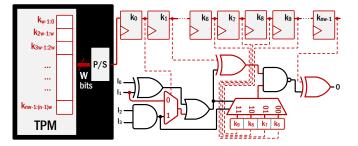

Fig. 5: Logic Locking Key Initialization from TPM.

how many output pins, and more importantly (2) for how many of the input patterns, the primary output (PO) will be corrupted once the key is incorrect. Usually, the output corruption is measured in terms of the hamming distance (HD) between the correct and the wrong output. Ideally, a 50% hamming distance is considered the highest deviation. Based on the location, structure, count, intercorrelation, etc., of the key-based XORs/MUXs/LUTs that are engaged for locking purposes, the corruptibility will change. Corruptibility directly affects the resiliency of the countermeasures against the existing attacks. For instance, if the corruptibility is low, it allows the adversary to look for a specific way for only those POs affected or those specific input patterns that produce output corruption. For a well-designed logic locking countermeasure, the corruptibility must be high to avoid such vulnerabilities.

As demonstrated in Fig. 4, the secret of logic locking, referred to as the key, must be provided to recover the correct functionality of the locked circuit. The key initialization of logic locking must be accomplished at a trusted facility and will be stored in TPM after the fabrication. Hence, the key management infrastructure around logic locking determines how the key will be initiated [36], [37], [38]. At power UP of a locked IC, as a part of the boot process, the content of TPM must be read and loaded into temporary registers connected to the locked circuit<sup>3</sup>. Fig. 5 shows a simple example of key initialization structure when logic locking is in place. Building the competent and secure infrastructure for key initiation<sup>4</sup> has been studied tremendously in the literature [36], [37], [38], [39], [40], [41], [42], whose details can be found in [43]. This part of the design consists of (1) TPM that consists of the logic locking key, (2) TPM wrapper which serializes the logic locking key via parallel-in to serial-out (P/S) module, and (3) temporary registers that stores the logic locking key while the IC is power ON, and (4) all infrastructure or customized cell required for securing the logic around key registers.

3. This is when the logic locking key size is large enough (In the range of 1k-2k key bits). For smaller key sizes, range of <200, although not recommended for incurred routing and overhead challenges, the key could be simultaneously loaded from the TPM with no shift process, but still needs to be registered for testability purposes.

4. In these infrastructures, regardless of the logic locking technique, different factors must be considered, e.g., the mechanism of key loading, integrating of key registers with DFT structure, removing the key leakage possibility through the scan chain, retaining the test coverage at high rates, etc.

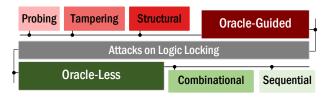

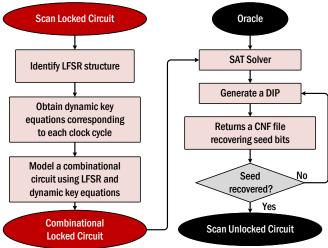

# 2.2 Models/Assumptions in Attacks on Logic Locking

Based on the threat models and assumptions evaluated in the de-obfuscation attacks on logic locking, the attacks could be categorized into different sub-groups. From a malicious end-user point-of-view, some of the attacks require access to one *additional* activated version of the fabricated circuit (atleast two in total: one for reverse-engineering and obtaining the locked netlist, and one as the reference known as oracle). This group of attacks could be referred to as **oracle-guided** attacks. On the other hand, those attacks with no need for having access to the oracle are called **oracle-less** attacks. During the last decade, most of the attacks are members of oracle-guided attacks. However, in many real cases, the adversary cannot obtain one additional activated chip, and the fulfillment of this requirement is hard to be achieved. So, the adversary has to rely on only oracle-less attack models.

Many of the de-obfuscation attacks are **invasive**. They require access to the netlist of the chip. Acquiring the netlist of the chip could be accomplished differently at various stages of the IC supply chain, as demonstrated in Fig. 2. For instance, the malicious end-user as the adversary can obtain the fabricated IC from the field/market, and then reconstructs the netlist through physical reverse engineering (orange path), in which the main steps of physical reverse engineering are de-packaging, delayering, imaging, image (of metal layers) processing, and re-constructing the netlist. In this case, during the physical reverse engineering, since the key is stored in TPM, it will be wiped out in the depackaging stage, and the obtained netlist would be locked.

Regarding the obtained (reverse-engineered) netlist, the same happens in all other cases, and the extracted netlist would be the locked version with no (correct) key. Another example is when the adversary might be at the foundry, and once they receive the GDSII of the chip from the design house to be fabricated, the GDSII is provided without the correct key (locked). In this case, although no delayering or physical infiltration is required, GDSII is required to be accessed and evaluated for netlist extraction, thus we consider it a *weak* invasive model. Even while the adversary is a rogue insider in the design house, except verification engineer<sup>5</sup> who needs the key for verification purposes, there is no necessity of sharing the key for stages like integration, synthesis, floorplanning, etc., showing that the obtained design is available with no key.

Unlike invasive attacks, there exists a very limited number of **semi-invasive** and **non-invasive** de-obfuscation attacks. In these attacks, the adversary relies on optical probing, such as electro-optical probing (EOP) and electrooptical frequency management (EOFM). Such attacks focus on pinpointing and probing the logic gates and flip-flops of the circuits containing the secrets. So, regardless of the logic locking technique used in the circuit, this group of attacks, which will be discussed through the paper, would be able to be a real threat for revealing the security assets like logic locking key.

The availability of design-for-testability (DFT) structure, i.e. scan chain architecture, for testability/debug purposes in ICs opens a big door for the attackers to assess and break logic locking techniques. Hence, many of the attacks

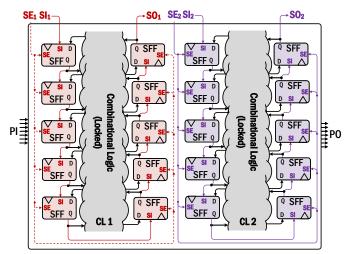

Fig. 6: Design for Testability (Scan Chain) Architecture in ICs.

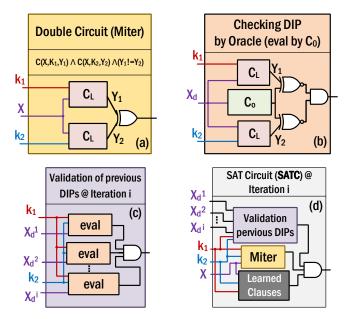

on logic locking assume that the scan chain is OPEN. Fig. 6 shows a simplified scan architecture with two chains. Assuming that the scan chain is *OPEN*, SE, SI, and SO pins would be available. So, the adversary can reach (control and observe) each combinational part, e.g.  $CL_1$  and  $CL_2$  in Fig. 6, whose FFs are part of the scan chain. The scan chain access allows the adversary to divide the de-obfuscation problem into a bunch of much smaller sub-problems (each CL), and assess them independently. However, it is very common for an IC to limit/restrict access to the scan chain for security purposes. But, even while **the access to the scan chain is NOT OPEN** (e.g. SO pins are burned), some other de-obfuscation attacks have studied and demonstrated the possibility of retrieving the correct key/functionality of the locked circuit via primary inputs/outputs (PI/PO).

Furthermore, the adversary located at the foundry might have the capability of priming and manipulating the GDSII to insert hardware Trojan for different purposes, such as key leakage through PO after the activation. The capability of inserting stealthy Trojans around the logic locking circuitry will be able to (1) disable the test access or (2) retrieve the logic locking key through PO. Hence, the capability of adding hardware Trojans when logic locking is in place, and being non-detectable by Trojan detection techniques could be a part of adversary capabilities that required meticulous consideration by the designers.

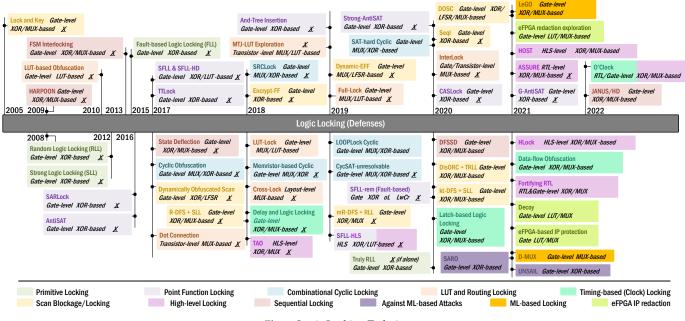

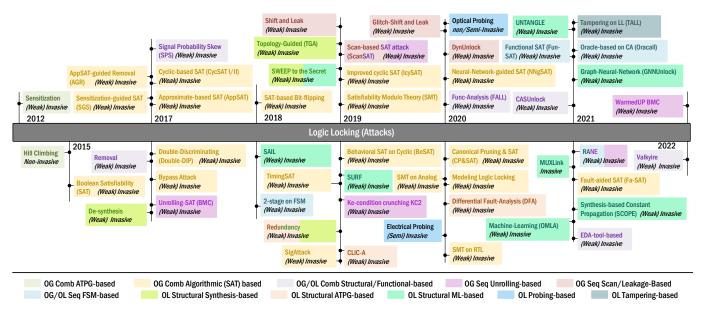

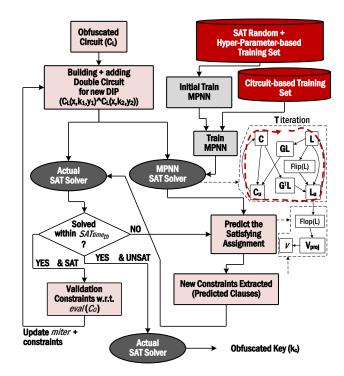

# **3** LOGIC LOCKING: COUNTERMEASURES

Starting 2008, numerous logic locking techniques have been introduced in the literature each trying to introduce a new countermeasure against the existing de-obfuscation attacks. Fig. 7 demonstrates a top view of existing notable logic locking techniques introduced so far. Based on the previously discussed basics and definitions of logic locking, we categorized them into different groups: (1) primitive, (2) point function, (3) cyclic, (4) LUT/routing, (5) scanbased locking/blocking, (6) sequential/FSM, (7) timingbased, (8) eFPGA-based, and (9) high-level (RTL/HLS). The main specification of any member of each countermeasure is illustrated in Fig. 7. In this section, regardless of the

<sup>5.</sup> We assume that the verification team is always trusted.

Fig. 7: Logic Locking Techniques.

existing successful attacks, we will briefly review the main specification of each logic locking category.

3.1 Primitive Logic Locking

The first group of countermeasures on combinational circuits is primitive techniques, including EPIC a.k.a. random logic locking (RLL) [11], strong (interference-based) logic locking (SLL) [12], and fault-based logic locking (FLL) [44]. For example, in EPIC (RLL), as its name implies, XORbased key gates will be inserted at some arbitrarily chosen points in the circuit. All primitive techniques are XORbased and implemented at the gate level. Since a locked circuit initiated with an incorrect key corrupts the PO by propagating errors at POs, in SLL and FLL, some features of automatic test pattern generation (ATPG) tools and testability specification, such as controllability/observability, and faults propagation/masking have been used for selecting the location of XOR-based key gates. For instance, in SLL [12], specifications like key-gates exclusion, isolation, cascading (running), mutability, and convergence have been examined, thereby by forming an interference graph of key gates, the best candidates are selected for key gate insertion, helping to enhance the strength of the logic locking against testing-based attacks (in comparison with RLL). However, using these features results in a notable reduction of corruptibility in SLL and FLL compared to that of RLL. In addition, in [42], a truly RLL has been defined that relies on XOR/XNOR insertion around inverters or buffers that is for randomly locking of signal polarities. Table 2 summarizes the specification of this breed of logic locking, showing that all are attacked by the Boolean satisfiability (SAT) attack, discussed in §4.1.2.

# 3.2 Point Function Logic Locking

The main aim of point function techniques is to minimize the number of available input patterns showing that a

**TABLE 2:** Specification of Primitive Logic Locking Techniques.

| Logic Locking | Mechanism                                                                      | Overhead Corrupt | Attacked by                |

|---------------|--------------------------------------------------------------------------------|------------------|----------------------------|

| RLL [11]      | Insertion of XOR key gates at <i>random</i> places                             |                  | ATPG:§4.1.1,<br>SAT:§4.1.2 |

| FLL [12]      | Insertion of XOR key gates at <i>lower</i> testable points                     |                  | SAT:§4.1.2                 |

| SLL [44]      | Interference-based key gate<br>insertion (non-mutuable,<br>non-isolated, etc.) |                  | SAT:§4.1.2                 |

| TRLL*1 [42]   | Insertion of XOR key gates at buffers and inverters                            |                  | SAT:§4.1.2                 |

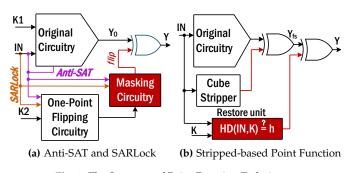

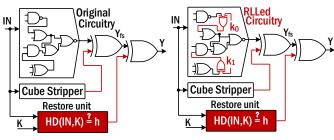

specific key is incorrect<sup>6</sup>. This breed was the first attempt against the Boolean satisfiability (SAT) attack, which can prune the keyspace by ruling out the incorrect keys in a fastconvergence approach [45], [46]. In the literature, this group of logic locking techniques is known as provably logic locking techniques. A logic locking technique is *provably* secure once they are algorithmically resilient (cannot be broken) against any type of I/O query-based attacks. SARLock and Anti-SAT are the very first logic locking techniques in this category [47], [48]. As demonstrated in Fig. 8(a), the main structure of point function techniques relies on a *flipping* (corrupting) circuitry that flips (corrupts) the limited PO(s) only for a very limited number of input patterns (e.g., 1) per each incorrect key. Also, a masking/restore (correcting) circuitry has been engaged in point function techniques to re-flip the impact of flipping circuitry, guaranteeing the correct functionality when the correct key is applied.

Point function techniques could be applied on the function-modified (stripped) version of the circuit, known as stripped function logic locking [51]. In such techniques, the original part is modified, and in at least one minterm, the (affected) POs are *ALWAYS* flipped/corrupted. This is done

6. The best case is ONE input pattern per each incorrect key.

TABLE 3: Specification of Point-Function Logic Locking Techniques.

| Logic Locking  | Mechanism                                                                                                                 | Overhead                                | Corrupt                                 | Attacked <sup>*1</sup> by                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------|

| SARLock [47]   | Adding flipping circuit to corrupt only ONE input pattern per<br>each incorrect key + masking circuit for correct key     |                                         |                                         | Removal:§4.1.3.1,<br>Approximate:§4.1.2.2, EDA-<br>based:§4.1.3.5, Bypass:§4.1.2.3      |

| AntiSAT [48]   | Merging of ANDed two toggled functions (g & $\bar{g})$ as the flipping+masking circuitry together                         |                                         |                                         | SPS/Removal:§4.1.3.2,<br>Approximate:§4.1.2.2, EDA-<br>based:§4.1.3.5, Bypass:§4.1.2.3, |

| And-Tree [49]  | hard-coded AND trees as flipping circuitry + a generic masking circuitry                                                  |                                         |                                         | CASUnlock:§4.1.3.4, EDA-<br>based:§4.1.3.5                                              |

| TTLock [50]    | SARLock + Stripping original circuit for one minterm                                                                      |                                         |                                         | EDA-based:§4.1.3.5,<br>GNNUnlock:§4.3.3,<br>FALL:§4.1.3.3                               |

| SFLL-HD [51]   | SARLock + Stripping original circuit for $d = {}^{k}C_{h}$ minterms ( <i>h</i> : HD and <i>k</i> : key size)              |                                         | variant (w.r.t. h)                      | EDA-based:§4.1.3.5,<br>GNNUnlock:§4.3.3,<br>FALL:§4.1.3.3                               |

| SFLL-flex [51] | Adding the flexibility of protecting user-defined input patterns in a point-function manner + LUT-based restore circuitry | variant (w.r.t. user-<br>defined list)  | variant (w.r.t. user-<br>defined list)  | EDA-based:§4.1.3.5                                                                      |

| SFLL-rem [52]  | removing logic for creating the corruption based on fault inser-<br>tion + a generic restore circuitry                    |                                         | variant (w.r.t. s-a fault location)     | EDA-based:§4.1.3.5                                                                      |

| G-AntiSAT [53] | Merging of ANDed two toggled functions (f & g) as the flip-<br>ping+masking circuitry together                            |                                         | variant (w.r.t. specs of f & g)         | EDA-based:§4.1.3.5                                                                      |

| S-AntiSAT [54] | App-level input pattern protection + generic restore circuitry                                                            | variant (w.r.t. input<br>patterns list) | variant (w.r.t. input<br>patterns list) | EDA-based:§4.1.3.5                                                                      |

| CAS-Lock [55]  | Variant AND-OR tree as variant corruptible circuitry                                                                      |                                         | variant (w.r.t. OR gates)               | EDA-based:§4.1.3.5,<br>CASUnlock:§4.1.3.4                                               |

Fig. 8: The Structure of Point Function Techniques.

using *cube stripper* module as demonstrated in Fig. 8(b). The *restore* unit builds the flipping and masking circuitry. In the stripped function techniques, for each incorrect key, there exists a very limited number of input patterns (e.g. 1) *plus* one extra input pattern (caused by the stripped function) that corrupts the POs (double point corruption). In fact, approaches with no stripping accomplish the flipping at one point (one input pattern per an incorrect key), while others with enabled stripping do the flipping at two points.

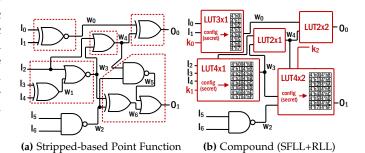

Point function techniques could be categorized as XORbased techniques. In SFLL-flex [51], LUTs are also engaged for minterm generations of corruption/correcting sub-circuits. Except for SFLL-HLS [56] that is implemented at the high-level (HLS), all techniques in this category are implemented at the gate level (post-synthesis). Since the point function sub-circuitry will be added for a limited (e.g. 1) number of POs and corrupts the PO for a very limited number of input patterns, the corruptibility of this breed of obfuscation is very low. However, there also exist more recent point function techniques that try to overcome the low corruptibility of such techniques with the introduction of different flipping (corrupting) circuits [53], [54], [55]. Table 3 summarizes the main specification of point function techniques. As shown, two new studies, i.e., sparse prime implication and Valkyrie (EDA-based) break all the variants in this group, showing the big structural issue behind this breed of logic locking.

# 3.2.1 Compound Logic Locking

The point function logic locking limits the corruption per each incorrect key to (i) a very little set of input patterns, and (ii) observable at a very little set of POs<sup>7</sup>. Hence, this breed suffers from a very low output corruption that significantly undermines its strength. Hence, a new paradigm was first introduced after point function techniques, in which the composition of different logic locking has been discussed, known as **compound** logic locking techniques. In compound logic locking, two or more different logic locking techniques can be used and applied simultaneously to a circuit if and only if none of them weaken the other ones. For instance, since the locking parts of the point function techniques are completely decoupled from the original part, as demonstrated in Fig. 8, and since the primitive logic locking techniques provides high corruptibility, as demonstrated in Fig. 9, these two can easily be combined to mitigate the lowcorruptibility issue of point function techniques, and also getting the benefit of high resiliency from point function techniques.

The concept of compound logic locking can be used for any feasible combination. For instance, in [57], a bilateral logic encryption has been introduced in which where a

<sup>7.</sup> The best case (in terms of enhancing the security) is that *ONE* input pattern can only rule out *ONE* incorrect key, and the corruption per each incorrect key can be witnessed at only *ONE* PO.

(a) Stripped-based Point Function (b) Compound (SFLL+RLL)

Fig. 9: The Structure of Compound Logic Locking Techniques.

TABLE 4: Specification of Compound Logic Locking Techniques<sup>\*1</sup>.

| Logic<br>Locking | Mechanism                                      | Overhead Corrupt | Attacked by                                            |

|------------------|------------------------------------------------|------------------|--------------------------------------------------------|

| X+Y              | Combination of prim-<br>itive + point function |                  | compound<br>attacks:§4.1.2.4,<br>Approximate: §4.1.2.2 |

\*1: This table is only for primitive + point function techniques.

X: Any primitive logic locking technique

Y: Any point-function logic locking technique

low-corruption logic locking technique and a routing-based approach have been integrated to show the effectiveness of compound logic locking against a wider range of attacks. Table 4 shows general definition of compound techniques.

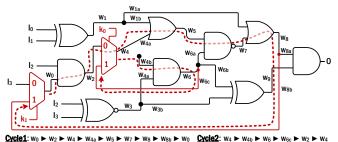

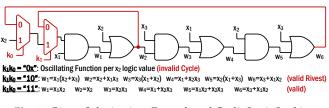

# 3.3 Cyclic-based Logic Locking

As its name implies and as shown in Fig. 10, cyclic logic locking will add key gates that control the possibility of adding/removing combinational cycles into the circuit. Having combinational cycles will add difficulties for the CAD tools (like synthesis and timing analysis) to deal with such circuits. Many CAD tools do not allow the designers to have combinational cycles in the circuit. However, the designer would be able to handle the combinational cyclic paths during the physical design in a manual manner, like adding constraints for false paths. Hence, combinational cycles are used commonly as a means of logic locking recently. In cyclic-based logic locking, different approaches are considered through different studies:

(i) <u>Adding false cycles</u>: In this case, similar to examples demonstrated in Fig. 10, some combinational cycles have been added into the design that should not be remained once the circuit is unlocked [58]. Having such cycles in the design creates uncertainty, glitches, and malfunction while the correct key is not provided.

(ii) <u>Adding misguiding combinational cycles</u>: Since the design must have no combinational cycles by itself, some approaches engage a set of valid misguiding combinational cycles, such as Rivest circuits [59] as shown in Fig. 11, to violate such basic assumption [60], [61], in which cycles are part of the original functionality. However, templatebased logic sub-circuits will be used for building this kind of cycle in a design that makes them vulnerable to structural analysis.

(iii) *Exponential increase of cycles*: To increase the complexity of cyclic-based logic locking, some studies have been evaluated the possibility and techniques that can be applied

Fig. 10: An Example of Cylic Obfuscation using 2-to-1 MUXes.

Fig. 11: Rivest Sub-circuit as Decoy-based Cyclic Logic Locking.

to exponentially increase the number of cycles *w.r.t.* the number of feedbacks [60], [62]. Exponentially increasing the number of cycles, will exponentially enhance the complexity of cyclic analysis. However, the existing approaches will also raise the area overhead significantly.

We are also witnessing some other studies that are using other techniques for increasing the complexity of cyclicbased logic locking, such as the implementation of cycliclocking using memristor-CMOS logic circuits, and inserting cycle pairs (duplicating sub-circuits), which are useful for hiding and misguiding the adversary for any kind of analysis on added/inserted cycles [63], [64], [65].

TABLE 5: Specification of Cyclic Logic Locking Techniques.

| Logic Lock-<br>ing                 | Mechanism                                                                                                                            | Overhead Corrupt | Attacked by                        |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------|

| Cyclic [58]                        | adding false combinational cycles into the circuit                                                                                   |                  | CycSAT:§4.1.2.5                    |

| SRCLock<br>[60]                    | exponentially increasing<br>false combinational cycles<br>w.r.t. the number of<br>feedbacks                                          |                  | <br>CP&SAT:§4.1.2.7                |

| memristor-<br>based cyclic<br>[63] | unresolvable combina-<br>tional cycles + memristor<br>cells for camouflaging<br>cycles                                               |                  | iCySAT:§4.1.2.5                    |

| CycSAT-<br>Unresolvable<br>[61]    | unresolvable combina-<br>tional cycles                                                                                               |                  | iCySAT:§4.1.2.5,<br>BeSAT:§4.1.2.5 |

| SAT-hard<br>cyclic [62]            | exponentially increasing<br>false combinational cycles<br>w.r.t. the number of<br>feedbacks + rivest cycles +<br>non-occuring cycles |                  | NONE                               |

| LOOPLock<br>[64]                   | creating pairs of cycles that<br>increasing the complexity<br>of cycle analysis                                                      |                  | NONE                               |

In general, since re-routing is required to generate the combinational cycles, all cyclic logic locking techniques use key-based MUX gates at different levels of abstraction. Also, in some cases, key-based XOR gates are used to build the model. All existing cyclic logic locking techniques are implemented at the gate level or transistor level. Since rerouting increases the correlation of wiring in different logic cones of the circuit, the corruptibility of this group of logic locking would be high. Table 5 shows the main specification of this breed of logic locking. Although some of these techniques are not broken so far, they are not considered as a mainstream in logic locking since it results in challenging industry adoption specifically in implementation and physical based EDA tools.

# 3.4 LUT/Routing-based Logic Locking

Some logic locking techniques derive the benefit from the full configurability of look-up-tables (LUTs). Relying on the fact that a *u*-input LUT can build all  $2^{2^u}$  possible functions, as demonstrated in Fig. 4, in existing LUT-based logic locking techniques, some actual logic gates of the original design are replaced with LUTs (same size or larger LUTs), and the initialization (configuration) values of the LUTs is considered as the secret (key) and would be initiated after the fabrication. In existing LUT-based logic locking, the followings have been investigated as the crucial factors [66], [67], [68], [69]:

(i) <u>Size of LUTs</u>: A point-to-point LUT-based replacement has been implemented in the existing LUT-based techniques, in which each selected gate will be replaced by a *same-size* (LUT2x1, LUT2x2 in Fig. 12) or *larger* (LUT3x1, LUT4x1, and LUT4x2 in Fig. 12) LUTs. Enlarging LUTs (Increasing the number of inputs) will exponentially increase the complexity of the logic locked circuit, however, it also increase the area/power overhead exponentially. In enlarged LUTs, the extra (unused) inputs can be used as the key to expand the complexity space (e.g.,  $k_{0:2}$  in Fig. 12).

(ii) <u>Number of LUTs</u>: The number of gates selected to be replaced with same-size/larger LUTs directly affects the complexity of the logic locked circuit, either functionally or structurally. However, similar to the side-effect of LUT size, using more LUTs will significantly increase the overhead of the logic locking approach.

(iii) *Replacement strategy*: The location of replacement in LUT-based logic locking plays a crucial role in making the resultant circuit more complex in the domain of logic locking. The work LUT-lock [67] has investigated how a good replacement strategy can render a higher grade of complexity while a heuristic approach has been used.

In general, although LUT-based logic locking can provide more reliable resilience against existing attacks, it extremely suffers from incurred overhead, which limits the application of this breed of logic locking. The Existing LUTbased techniques are all implemented at the gate level or transistor level and based on the placement strategies used for LUT insertion, the corruptibility of these techniques is also high.

Similar to LUT-based logic locking, which can be built using a MUX-based (tree of MUXes) structure, numerous studies have exploited the concept of MUXes for another breed of logic locking, known as routing-based locking. In routing-based locking, false/decoy/invalid paths could be added using re-routing modules in different levels of abstraction. For instance, at the gate level of abstraction, MUXes could be used for re-routing, and at layout-level,

Fig. 12: LUT-based Logic Locking Technique.

(a) Crossbar-based Routing-based Locking

(b) Logarithmic-based Routing-based Locking

Fig. 13: Routing-based Locking Technique.

metal-insulator-metal (MIM) could be used for re-routing between metal layers as a means of logic locking.

Dealing with the complexity of the routing modules has been evaluated for a long time as a part of physical P&R in both FPGAs/ASICs [70], [71], [72]. Hence, this complexity is borrowed here as a means of locking in these techniques. But the concept of routing-based locking was firstly derived from the usage of wiring/connection concealment in splitmanufacturing techniques [73], [74], [75]. In these techniques, different forms of re-routing, such as perturbation, lifting nets, etc., have been engaged to hide the connections between BEOL and FEOL. Hence, a similar approach has been used in a circuit for locking purposes. For instance, Fig. 13 shows two different routing-based techniques, i.e. Crosslock [76] and full-lock [77]. As demonstrated, in routingbased locking, some wires of the design will be selected and the routing module, whose configuration is the locking key, will conceal the connection between sources and sinks.

Unlike point function techniques that decrease the pruning power of the existing I/O query-based attacks (e.g., the SAT attack) by exponentially increasing the required number of I/O pairs, routing-based techniques show how a routing module can extremely increase the complexity of design per each stimulus [77]. Routing-based locking techniques have investigated different factors that significantly affect the outcome of this breed of locking solutions as listed here:

(i) Abstraction Layer of Implementation: Routing modules can be implemented at different layers of abstraction. Moving towards lower levels (e.g., layout) significantly increases the implementation efforts and challenges, however, if implemented correctly at lower levels, it incurs considerably lower overhead. Techniques like Cross-lock and interconnect-based locking are implemented at the layout level [76], [78]. Full-lock implements routing module at the gate level [77]. An extension on Full-lock is also implemented at gate-level [79], and Interlock is also implemented at both gate level and transistor-level [80].

(iii) *Topology of Routing Modules*: Once a routing module is in place, the topology of interconnections is a determining characteristic. Hence, in routing-based locking techniques, different topologies have been used, such as crossbar in [76], [78], logarithmic networks in [77], [79], [80], [81], and irregular [82]. The type of topology can directly affect the resiliency of the countermeasure against different attacks. For instance, logarithmic networks with deeper layers can extremely increase the complexity of the model in any graphbased and routing-based analysis. However, the topology can negatively affect the overhead, particularly delay of timing paths selected for routing locking.

(ii) <u>Cycle-involvement in Routing-based Locking</u>: Based on the wire selection in routing-based locking techniques, cycles might be created once an incorrect key will be applied. For instance, as shown in Fig. 13, the output of g2/LUT2<sub>2</sub> is back and connected to the input of routing module. Although the creation of cycles will increase the complexity of locking techniques, to avoid any design/implementation flow challenges dealing with cycles, in more recent techniques [79], [80], since actual timing paths of the design are embedded into routing modules, there exists no possibility of cycle creation.

(iv) Logic Embedding in Routing Module: To increase the complexity of routing modules, recent works [77], [79], [80] have investigated the embedding of logic gates into (switch) layers of routing module. For instance, switch boxes of LogNet in Fig. 13(b) provides configurable inversion. Hence, Gates like g1 and g5 is toggled (stripped) and the LogNet will recover the correct logic values. Hence, in these techniques, with the full configuration capability, stripping the functionality of the original circuit would be an extra available option.

Table 6 summarizes the specification of routing-based locking countermeasures. In comparison with other breeds, routing-based locking will incur higher overhead. However, more recent studies, such as coarse-grained eFPGA-based IP redaction (§3.9) show that this form of locking that inherits full reconfigurability for locking purposes still has significant potential as a means of logic locking. As demonstrated, all existing routing-based locking solutions are broken, mostly by very recent ML-based attacks described in 4.3.3.

**TABLE 6:** Specification of Routing-based Locking Techniques.

| Logic Locking            | Mechanism                                                                                                                | Overhead Corrupt | Attacked by                    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|

| Cross-Lock<br>[76]       | Insertion of key-based<br>layout-level cross-bar with<br>combinational cycles                                            |                  | CP&SAT,<br>NNgSAT:<br>§4.1.2.7 |

| Dot Connec-<br>tion [78] | Insertion of key-based<br>layout-level cross-bar with<br>combinational cycles                                            |                  | CP&SAT,<br>NNgSAT:<br>§4.1.2.7 |

| Full-Lock [67]           | Insertion of gate-level key-<br>based logarithmic routing<br>modules with inversion<br>stripping                         |                  | CP&SAT,<br>NNgSAT:<br>§4.1.2.7 |

| Modeling<br>routing [67] | Insertion of gate-level key-<br>based logarithmic routing<br>modules with logic embed-<br>ded                            |                  | Untangle:<br>§4.3.3            |

| InterLock [67]           | Insertion of gate or<br>transistor-level key-<br>based logarithmic routing<br>modules with logic<br>embedded + stripping |                  | Untangle:<br>§4.3.3            |

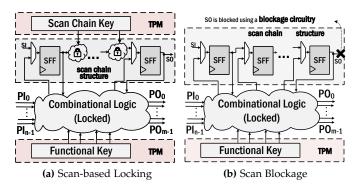

# 3.5 Scan Chain Logic Locking/Blocking

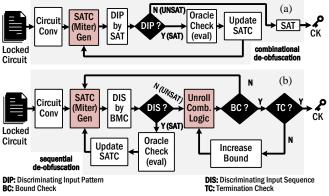

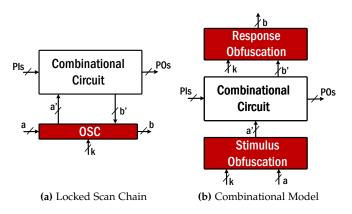

Providing the access to the internal parts of the circuit for test/debug purposes is almost inevitable in modern/complex ICs. As discussed previously in §2.2, designfor-testability (DFT)-based synthesis in ASIC design flow provides this capability for the designers by adding scan (register) chain structures into the circuit. The DFT-based scan chain architecture has been widely used in most modern ICs. Even in cryptographic circuits, which have very sensitive information, such as encryption key, to have a high fault coverage, the test/debug step requires access to the scan chain to control and observe the internal states of the design-under-test (DUT). The full controllability and observability requirement in DFT-based (scan-based) testing, however, might pose security threats to ICs with security assets, such as locked circuits that keep their own secret, i.e., the unlocking key. Hence, DFT access allows the adversary to split and divide the bigger problem into a set of independent smaller problems by splitting the whole circuit into c smaller and only combinational logic parts, whose access to their register elements are available via scan chains (e.g., CL1 and CL2 of Fig. 6 through  $\{SI_1, SE_1, SO_1\}$  and  $\{SI_2, SE_2, SO_2\}$ , respectively). We further demonstrate that scan chain access availability is one of the main assumptions of the SAT attack, discussed in  $\S4.1.2.1$ .

Since restricting the scan chain access can enlarge the problem space domain from small combinational subcircuits to a whole large sequential circuit, a breed of logic locking techniques focus on different methodologies that only and primarily target the locking of the scan chain architecture, known as scan-based logic locking techniques [83], [84], [85], [86], [87], [88]. By using these techniques, the scan chain pins, i.e. scan-enable (SE), scan-in (SI), and particularly scan-out (SO) would be limited/restricted for any unauthorized access, and these approaches do not allow the adversary to get the benefit these pins, and they lose the chance of direct/independent controlling/observing the combinational parts of the circuit. Similar to scan-based logic locking techniques, some approaches BLOCK the access to the scan chain pins, particularly SO [36], [37], [38], [40], [42], called scan blockage techniques. The scan block-

Fig. 14: Scan Chain Locking/Blocking Technique.

age will happen based on a sequence of specific operations in the scan chain structure. For example, assuming that (part of) the key is loaded into the scan chain after activation, switching *SE* to 1 (enabling shift mode) might be perilous. Hence, shift operation would be limited after the activation. Fig. 14 shows the top view of both scan locking and scan blockage techniques. Compared to the scan-based logic locking techniques, the scan blockage techniques incur less area overhead. However, they have some limitations during the test phase, such as limiting the functional test and increasing the test time and complexity.

The following describes the main specifications and principles of scan chain locking/blockage techniques:

(i) *Combination with Functional Logic Locking*: Scan chain locking/blockage is orthogonal to other functional logic locking techniques. In fact, the scan-based logic locking techniques only lock the scan structure. So, even while an incorrect key is initiated in the circuit, it only affects the scan chain functionality and has no impact on the functionality of the circuit. Hence, these techniques need to be combined with one of the other discussed combinational logic locking techniques, and the existing techniques. Some techniques use RLL [37], some other techniques use SLL [38], [83], [89], and one scan blockage technique is combined with truly-RLL (TRLL) [42]. Hence, the corruptibility of these approaches is dependent on the engaged functional logic locking techniques.

(ii) *Implementation Abstraction Layer*: Since scan chain locking/blockage techniques must be applied to the scan chain structure, they only could be done after design-fortestability (DFT) synthesis. So, these techniques could be implemented at the gate level, the transistor level, or the layout level. All the existing techniques are implemented at the gate level.

(iii) <u>Test Coverage/Overhead</u>: Scan chain locking/blockage can negatively affect the testability metrics, e.g., test coverage, resulting in the reduction of reliability of the circuits. Hence, one crucial criterion in this breed is to keep the test coverage as close as possible to that of the original circuit before scan locking/blocking. Additionally, in some of the blockage techniques, extra test pins have been added to support high testability coverage and efficient resiliency [36], [37], [38], [40]. However, adding extra pins can extremely increase the die size of the manufactured chip.

| Logic Locking                                 | Туре               | Mechanism                                                                                                       | Overhead | Attacked by             |

|-----------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------|----------|-------------------------|

| DOS [83], [89]                                |                    | Dynamic LFSR-based Shuf-<br>fling and Toggling with<br>Shadow Scan Insertion                                    |          | ScanSAT:<br>§4.2.3.1    |

| Encrypt-FF<br>[84]                            | Locking<br>by XOR  | XOR-based key gate inser-<br>tion within the scan chain                                                         |          | ScanSAT:<br>§4.2.3.1    |

| Robust design<br>for security<br>(R-DFS) [40] | Blockage           | A custom secure DFF for<br>key storage + SO blockage<br>circuitry for post-activation                           |          | shift&leak:<br>§4.2.3.3 |

| dynamic-EFF<br>[85]                           | Locking<br>by PRNG | Adding PRNG and mal-<br>functioning by PRNG for<br>incorrect keys                                               |          | DynUnlock:<br>§4.2.3.2  |

| Extended<br>R-DFS [37]                        | Blockage           | A custom secure DFF for<br>key storage + SO blockage<br>circuitry for post-activation                           |          | shift&leak:<br>§4.2.3.3 |

| seql [86]                                     | Locking<br>by XOR  | XOR-based key gate in-<br>sertion between functional<br>and scan chain paths                                    |          | ScanSAT:<br>§4.2.3.1    |

| kt-DFS [38]                                   | Blockage           | A custom secure DFF for<br>key storage + SO blockage<br>circuitry for post-activation                           |          | NONE                    |

| DisORC [42]                                   | Blockage           | SO Blockage circuitry with<br>full shift disable after acti-<br>vation + disabling shift +<br>oracle dishonesty |          | NONE                    |

| DOSC [88]                                     |                    | Dynamic LFSR-based Shuf-<br>fling and Toggling with<br>Shadow Scan Insertion                                    |          | NONE                    |

(iv) Locking Operation Method: In scan chain locking, the locking part can operate statically or dynamically. In the dynamic approach, components like LFSR and/or PRNG have been engaged that changes the configuration at run-time [83], [85], [88], [89]. However, in techniques with statically scan chain locking [84], [86], the configuration is always fixed. The dynamicity -if implemented correctly- is always a huge bar for the adversary, specifically, once they rely on I/O query-based attacks, and dynamicity invalidates all learned information acquired on previous acts and enforces the adversary to restart the process.

(v) *The Security of Scan Chain Architecture*: Scan chain locking/blocking brings some modification into the structure of scan chain(s). This modification particularly comes from scan blockage techniques. For instance, with a more robust scan chain architecture, the designer might integrate all regular FFs and key-dedicated FFs into a common scan chain. However, this can undermine the security of the logic locking key, regardless of locking techniques, if a leakage possibility could be found through the modified scan chain structure or cells. So, the security of the scan chain must be evaluated and guaranteed while scan chain locking/blockage is applied to the circuit.

Table 7 summarizes the main specification of existing scan-based locking/blocking techniques. At the moment, a combination of one scan-based logic locking or scan blockage with functional logic locking techniques shows high resiliency and received significant attention. Scan-based protection extremely increases the size and complexity of formulation for any attacking model on logic locking. We further discuss that this type of locking is an integral part of reliable and security-guaranteed logic locking techniques against all existing threats.

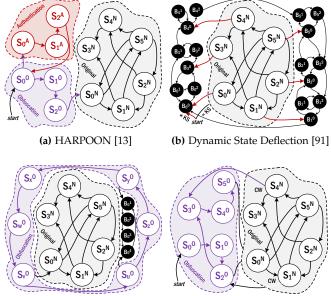

# 3.6 FSM/Sequential Logic Locking

One basic assumption in all previously discussed logic locking techniques' threat model is that the availability of the scan chain is NOT restricted. However, in a notable portion of real ICs/SoCs, this availability is blocked for critical security reasons. Assuming that the scan chain access is already limited/restricted, some logic locking techniques focus on locking the whole circuit, which could be considered as sequential logic locking techniques. Most of them focus on the locking of the state (FSM) of the circuit. In existing FSM locking techniques [13], [14], [90], [91], [92], [93], [94], [95], the original FSM has been targeted and altered in different ways, as demonstrated in Fig. 15: (i) adding few extra sets (modes) of states to the original state transition graph (STG), such as locking/authentication mode states, (ii) adding traps such as black hole, (iii) altering the deepest states of the circuit that makes the timing analysis longer and more complex, (iv) adding shadow states which acts like decoy states, and (v) making the FSM combinational fan-in-cone sub-circuitry key-dependent.

In the primitive FSM-based logic locking techniques, there exists no dedicated port/pin/wiring for key values, and the traversal sequence of these extra added states (sequence of input patterns), like traversal of locking/authentication modes, is the locking/authentication key, and a correct traversal allows the user to reach and traverse the original part of the FSM. Hence, unlike all other logic locking techniques, key inputs are implicitly added, and we can consider this form of logic locking as key-less logic locking. Also, the output generated by the correct traversal of authentication states serves as a watermark. In addition to these groups, a set of studies evaluate FSM locking without adding any extra state. However, the complexity and overhead (area) of this approach is higher compared to other schemes [92]. More recent FSM-based logic locking studies also evaluate the combination of state traversal and key-based logic locking [93], [94], [95]. Table 8 summarizes the main specifications of existing FSM-based logic locking techniques.

# 3.7 Behavioral Timing-based Locking

Unlike all previous techniques that focus on the functionality of the design, some logic locking techniques went one step further and lock the behavioral properties of the circuit, such as timing. For example, DLL [15] introduces a custom tunable delay and logic gate, demonstrated in Fig. 16(a) which could have different delays based on the value of the key. Since most of the CAD tools are dealing with Boolean nature, it would be hard for the adversary to deal with this form of ambiguity. Some more recent techniques use multi-cycle paths, key-controlled clock handling, and latch-based structure, in which the timing of the circuit would be changed in an asynchronous/clockgated manner [97], [98], [99], [100], [101]. For instance, in latch-based and asynchronous-based techniques [99], [100], the time of storage of data in the FFs are asynchronized and controlled with the key. More particularly in data flow obfuscation [100], as demonstrated in Fig. 16(c), key-based celement of asynchronous circuits has been used to control the timing/flow of data within the design. So, without 12

(c) Hardware Active Metering [90] (d) Interlocking Obfuscation [14]

#### Fig. 15: FSM Locking Technique.

TABLE 8: Specification of FSM-based Logic Locking Techniques.

| Logic Locking                | Mechanism                                                                                           | Overhead                 | Corrupt                     | Attacked by                         |

|------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|-------------------------------------|

| HARPOON<br>[13]              | Adding extra authenti-<br>cation and obfuscation<br>states before the origi-<br>nal initial state   | (w.r.t. size             |                             | RANE:4.2.2.2<br>Fun-SAT:<br>4.2.2.3 |

| FSM<br>Interlocking<br>[14]  | Adding traps per each<br>original state for incor-<br>rect key or sequence                          |                          |                             | Fun-SAT:<br>4.2.2.3                 |

| Active Meter-<br>ing [90]    | Adding extra obfusca-<br>tion states + black holes<br>for specific transitions                      | (w.r.t. size             | High at new extra states    | Fun-SAT:<br>4.2.2.3                 |

| Dynamic De-<br>flection [91] | Inserting code-word<br>transitions based on<br>input pattern + extra<br>states before initial state | (w.r.t. size<br>of added | High at new<br>extra states |                                     |

| FSM reconfig<br>[96]         | reconfigurable logic for<br>FSM circuitry (Only on<br>FPGA)                                         |                          |                             | NONE                                |

| DFSSD [93]                   | Adding faults at deep<br>states using counter +<br>point function                                   |                          |                             | NONE*1                              |

| JANUS/HD<br>[94], [95]       | Concealment of State<br>transition circuitry us-<br>ing a configurable con-<br>trol unit            |                          |                             | NONE                                |

\*1: It could be vulnerable to structural-based removal attack, if no camouflaging is in place for some locking gates.

having the correct key, the flow of data movement will be changed within the circuit, which consequently corrupts the functionality and may result in appearing some halt in the circuit.

The timing-based and latch-based technique shows promising results against different adversary' actions. However, due to the lack of full EDA (electronic design automation) tool support for asynchronous designs, replacing the flip-flops with latches and implementing asynchronous

Fig. 16: Behavioral Timing-based Locking: (a) Delay-based Locking [15], (b) Latch-based Locking [99], (c) Asynchronous Locking [100], (d) Clock-gated Locking [101].

TABLE 9: Specification of Timing-based Logic Locking Techniques.

| Logic Locking         | Mechanism                                                                                     | Overhead Corrupt | Attacked by  |

|-----------------------|-----------------------------------------------------------------------------------------------|------------------|--------------|

| Delay Locking<br>[15] | Insertion of tunable delay<br>buffers that control both<br>function and delay of key<br>gates |                  | SMT:§4.1.2.6 |

| Latch-based<br>[99]   | adding key-based latches + decoy-based latch insertion                                        |                  | NONE         |

| Data-flow<br>[100]    | controlling the data flow<br>using asynchronicity + de-<br>coy latches + decoy logic          |                  | NONE         |

| O'Clock [101]         | locking the clock gating<br>circuitry + transition-based<br>stripping functionality           |                  | NONE         |

latch-based designs raise burdensome challenges in the IC design process, and it makes the usage of asynchronicity almost impractical for complex SoCs. A very recent study, called O'clock, relies on widely-used clock-gating techniques and targets the clock-gating enabling circuitry for obfuscation purposes with full EDA-based support. One of the main features of these timing-based techniques is that they control and manipulate the time of data capturing at storage elements, i.e., at FFs. Hence, the adversary cannot track and follow the exact and correct timing of data capturing, and there is no additional benefit for the design team to restrict/block the scan chain. So, unlike the scan locking or blockage, they can keep scan chain available (imperative to perform in-field debug and test but exploited by SAT attack [45]) to the untrusted foundry and end-users while resisting a wider range of I/O query-based attacks, like SAT-based attacks. Table 9 summarizes the main specifications of existing timing-based logic locking techniques. As demonstrated, except for delay locking that is broken using a theory-based I/O query-based attack, called SMT attack [102], all others are not broken, showing the robustness of this breed of logic locking.

# 3.7.1 beyond-CMOS and Mixed-Signal Logic Locking

In comparison to CMOS technology, emerging technologies, such as spintronics, memristors, FinFet, CNTFETs, and NWFETs, which are also compatible to be integrated with CMOS technology, promise and provide unique properties that can be engaged for security purposes, features like variability/randomness, run-time reconfigurability or polymorphic behavior. The utilization of these features can help to obtain resilience against reverse engineering, to build unique PUF/TRN generation units, to protect IPs, and to build masking against side-channel leakage [103]. Hence, a set of existing logic locking (and more on camouflaging) techniques have used such technologies. Many of these approaches utilize these technologies to achieve (i) reconfigura*bility/dynamicity* that helps to invalidate continuous analysis on the locked circuit (requires frequent restart), (ii) resiliency against reverse engineering that helps against diverse acts by the adversary for revealing the secrets, such as probing or retrieving the unlocking key, or retrieving the netlist by the untrusted foundry. The utilization of emerging technologies for IP protection through logic locking can be summarized as follow:

(i) *Spintronic-based*: With a non-volatile switching mechanism and other related concepts like spin-transfer torque, spin electronics technology can provide both computation and storage/memory capabilities (STT) [104], [105], [106]. All-spin logic (ASL) for camouflaging [107], spintronics-based reconfigurable LUTs [68], [108], [109], [110], fully programmable polymorphism based on giant spin-Hall effect (GSHE) [111], [112] are some approaches that leverage this technology for locking+camouflaging at lower overhead compared to CMOS-based counterparts.

(ii) <u>Memristor-based</u>: Memristor-based (memory-resistor) cells are basically able to retain their internal resistive state w.r.t. the voltage/current applied, which can be used for building Boolean logic [113], [114]. In [63], [115], the concept of reconfigurable (polymorphic) cyclic logic locking has been proposed in which the memristor cell(s) has been used to protect against adversaries in the foundries and test facilities.

(iii) <u>FET-based</u>: Tunnel field-effect transistors, carbon nanotube field-effect transistors (CNTFET), and Nanowire FETs (NWFETs) are other leading emerging technology candidates to replace CMOS FinFET and DRAM technologies, which are compatible with CMOS technology [116], [117], [118], [119], [120]. Similarly, these technologies could be used for implementing polymorphic gates (PLG) as a means of locking+camouflaging [121], [122], [123], [124]. In [123], silicon nanowire (SiNW) FETs are utilized to implement different PLGs for making the locking part less traceable. The authors of [121] propose silicon NWFETs for camouflaging+locking, by using controlled ambipolarity of NWFETs, helping to build primitives like NAND, NOR, XOR, and XNOR functions.

Apart from beyond-CMOS technologies, some approaches also investigated the applicability and application of logic locking in analog and mixed-signal (AMS) circuits, which is a large subclass of analog ICs, including data converters, phase-locked-loops (PLLs), radio frequency (RF) transceivers, etc. [125], [126], [127], [128], [129], [130], [131]. Many of these approaches consider the locking of digital

Fig. 17: High Level Logic Locking Technique.

parts that directly or indirectly affects the analog side [125], [126], [131]. However, to expand the locking over both analog as well as digital sections, other approaches target modules like analog-to-digital or digital-to-analog (ADC/DAC) converters [127]. Another study uses chaotic computing and proposes a mixed-signal locking by adopting chaogate [132] to get two important advantages of this mechanism, i.e. (1) Ability to build all  $2^{2^2}$  functions of a 2-input Boolean gate using a single chaotic element (like LUT but at lower overhead), and (2) Dynamic function update capability [130]. At the layout level, few studies also investigate the sizing and hiding as a camouflaging approach by means of fake contacts in the active geometry of the layout components [129].

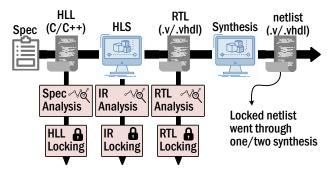

# 3.8 High-level Logic Locking

Although a high portion of existing logic locking techniques is implemented at the gate level (or even transistor/layout level), they may be incapable of targeting all semantic information (defined and described in higher level, e.g., RTL or HLS) since logic synthesis and optimizations will convert/simplify/twist much of it into the netlist. Hence, to (1) be able to directly target any algorithmic and semantic of the design for locking purposes, and (2) to get the benefit of synthesis and conversion done by the optimizations for twisting logic locking part into the original part(s), a bunch of recent studies utilizes new methodologies for locking at a higher level of abstractions [56], [133], [134], [135], [136], [137], [138], [139], [140].

Another advantage of high-level logic locking techniques is that they can potentially protect the design against a wider range of untrusted entities. As shown in Fig. 2, with the notion of insider threats (e.g., a rogue employee at the design house), high-level locking allows the design team to have the IP locked and protected from far earlier stages of IC design flow. As demonstrated in Fig. 17, high-level locking can be categorized into the following groups. Also, Table 10 covers the main specification of existing countermeasures in this breed of logic locking.

(i) <u>High-level Locking before Synthesis/Transition</u>: Some of the approaches apply the logic locking at the highest level (e.g., C/C++) code before synthesizing the design through the HLS steps [136]. In such cases, the HLL code provided to the HLS tool is already locked, and conversion/absorption/transformation on locked semantic will happen through (i) the HLS intermediate steps, including

(ii) *High-level Locking+Synthesis (HLS extension)*: Some studies implement and integrate locking with the intermediate steps of the HLS engine [56], [133], [135], [140]. Such approaches analyze intermediate representations (IRs) generated through the HLS flow and will extend these IRs by applying the locking part. In these approaches, the HLL code is not locked, but the RTL generated by the HLS tool is locked, and the locked RTL will face conversion/absorption/transformation through RTL synthesis

(iii) <u>Register-Transfer Locking (post-HLS or direct RTL)</u>: Techniques in this sub-group apply logic locking at RTL level, either on the output of the HLS engine, i.e. the RTL generated by the HLS tool [134], [138] or RTL designed/developed directly by the designers [139]. This group analyzes the specification of RTL (like abstract syntax tree) or other graph-based representation to find the best candidates for selection and locking, and then the locked RTL will go through the RTL synthesis.

(iv) *Compound Locking (High level + Gate level)*: We also witness a compound form of logic locking in which RTL locking and gate-level have been engaged as a single countermeasure. In [137], RTL locking is combined with a scan-based logic locking to thwart threats induced by both untrusted foundry and malicious users.

Moving from gate level to higher levels allows the designers to target higher order elements, such as semantic information: (1) <u>Constants</u>: Sensitive hard-coded information through the computation (e.g., filter coefficients, encryption IVs, etc.). (2) <u>Arithmetic Operation</u>: Critically determining functional arithmetic operation (e.g., multiplications, shifting, adding, subtraction, etc.). (3) <u>Conditional Branches</u>: Branches defining the execution flow (based on the control flow graph). (4) <u>Function Calls</u>: Important function calls that build the main hierarchy of the design. (5) <u>Memory Access</u>: Address, read, and write for the memory blocks with sensitive information. Based on these elements targeted for locking, all high-level logic locking techniques can provide high corruptibility. Table 10 summarizes the specification of existing logic locking at higher level.

# 3.9 eFPGA-based IP-level Locking