# Masked Accelerators and Instruction Set Extensions for Post-Quantum Cryptography

Tim Fritzmann<sup>1</sup>, Michiel Van Beirendonck<sup>2</sup>, Debapriya Basu Roy<sup>1</sup>, Patrick Karl<sup>1</sup>, Thomas Schamberger<sup>1</sup>, Ingrid Verbauwhede<sup>2</sup> and Georg Sigl<sup>13</sup>

<sup>1</sup> Technical University of Munich, TUM Department of Electrical and Computer Engineering,

Chair of Security in Information Technology, Munich, Germany

{tim.fritzmann,debapriya.basu-roy,patrick.karl,t.schamberger,sigl}@tum.de

<sup>2</sup> imec-COSIC KU Leuven

Kasteelpark Arenberg 10 - bus 2452, 3001 Leuven, Belgium

{michiel.vanbeirendonck,ingrid.verbauwhede}@esat.kuleuven.be

<sup>3</sup> Fraunhofer Institute for Applied and Integrated Security, Garching, Germany

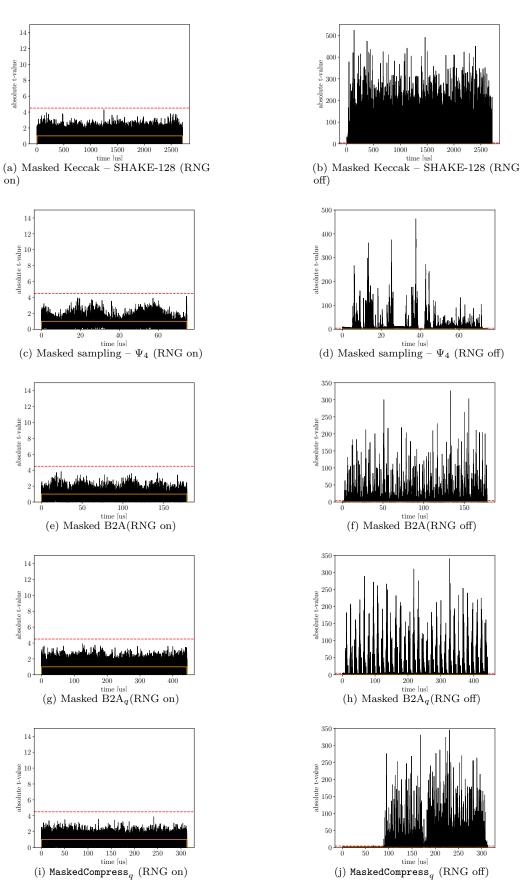

**Abstract.** Side-channel attacks can break mathematically secure cryptographic systems leading to a major concern in applied cryptography. While the cryptanalysis and security evaluation of Post-Quantum Cryptography (PQC) have already received an increasing research effort, a cost analysis of efficient side-channel countermeasures is still lacking. In this work, we propose a masked HW/SW codesign of the NIST PQC finalists Kyber and Saber, suitable for their different characteristics. Among others, we present a novel masked ciphertext compression algorithm for non-power-of-two moduli. To accelerate linear performance bottlenecks, we developed a generic Number Theoretic Transform (NTT) multiplier, which, in contrast to previously published accelerators, is also efficient and suitable for schemes not based on NTT. For the critical non-linear operations, masked HW accelerators were developed, allowing a secure execution using RISC-V instruction set extensions. With the proposed design, we achieved a cycle count of K:214k/E:298k/D:313k for Kyber and K:233k/E:312k/D:351k for Saber with NIST Level III parameter sets. For the same parameter sets, the masking overhead for the first-order secure decapsulation operation including randomness generation is a factor of 4.48 for Kyber (D:1403k) and 2.60 for Saber (D:915k).

**Keywords:** Post-quantum cryptography  $\cdot$  Kyber  $\cdot$  Saber  $\cdot$  masking  $\cdot$  RISC-V  $\cdot$  accelerators  $\cdot$  instruction set extensions

## Introduction

Rapid progress in the area of quantum computers drives the need for new cryptographic algorithms resistant against attacks that use quantum computers. While classical publickey cryptography, such as RSA and Elliptic Curve Cryptography (ECC), will be broken with a large-scale quantum computer, Post-Quantum Cryptography (PQC) refers to a set of algorithms that are supposed to be secure against cryptanalytic attacks using a quantum computer. To accelerate the transition from classical to quantum-secure cryptography, the National Institute of Standards and Technology (NIST) started a standardization process [Nat16] and recently selected seven algorithms as finalists and eight alternate candidates [AASA<sup>+</sup>20]. Out of the seven finalists, five schemes are based on the hardness of structured lattice problems. Lattice-based cryptography has become one of the most important PQC categories as it is characterized by a very high performance and relatively small ciphertext and key sizes. In the last years, there has been a strong focus on efficient implementations of PQC on constrained devices, with the ARM Cortex-M4 microcontroller as the main target platform [KRSS18, AABCG20, MKV20]. To increase the performance of such devices but keeping the flexibility of a SW solution, HW/SW codesign strategies were recently introduced for PQC [FSM<sup>+</sup>19, FSF<sup>+</sup>19, FDNG19]. A new trend is to use platforms based on RISC-V, which is an open Instruction Set Architecture (ISA) constructed using the reduced instruction set principles. The RISC-V initiative has led to a new processor design era, fostering the development of open-source processors and the integration of ISA extensions. In this context, related works developed ISA extensions for PQC achieving high performance and flexibility [AEL<sup>+</sup>20, FSS20].

While current PQC implementations claim to be resistant against timing Side-Channel Attacks (SCA), more advanced attacks (e.g. power or electromagnetic attacks) where the attacker has physical access to the device have been mostly neglected during the design of optimized implementations. In particular, Differential Power Attacks (DPA) are of major concern [KJJ99]. Simple Power Attacks (SPA) are very sensitive to noise, but DPA reduces the influence of noise by utilizing information from multiple measurements. Therefore, this work focuses on DPA protected PQC implementations.

**Related works.** Prior works already discuss DPA countermeasures for PQC and in particular for lattice-based cryptography. The first masked lattice scheme based on the Learning with Errors Problem (LWE) was proposed in [RRVV15], and subsequently improved in [RdCR<sup>+</sup>16]. Protection mechanisms for the GLP signature scheme were analyzed in [BBE<sup>+</sup>18] and blinding countermeasures for the signature scheme BLISS were developed in [Saa18]. A protected implementation of a predecessor of the NIST PQC second round scheme NewHope was proposed in [OSPG18], but security flaws were found in some of the underlying algorithms [VBDV21, BDH<sup>+</sup>21]. Later, the second round scheme qTESLA [GR19] and the signature finalist Dilithium [MGTF19] were protected. The Public-Key Encryption (PKE) / Key-Encapsulation Mechanism (KEM) finalist Saber [BDK<sup>+</sup>21] was masked for an ARM Cortex-M4. Concurrent to our work, [BGR<sup>+</sup>21] presented a masked implementation of Kyber on ARM Cortex platforms. Further works proposed higher-order conversions with prime modulus for the binomial sampling [SPOG19] and a fast protection mechanism for polynomial multiplications [HP21].

**Contributions.** Although there has been good progress due to all of these works, a clear picture of efficient countermeasures and related implementation costs is still not available for the NIST PQC finalists. In particular, NIST assumes that only one of the lattice-based PKE/KEM finalists Kyber, Saber, or NTRU will be standardized after the third round. In contrast to the other two lattice-based finalists, NTRU is not based on the Learning With Errors (LWE) problem and is considered less efficient than the other two competitors but has a longer history [AASA<sup>+</sup>20]. The selection of NTRU as a winner of the NIST standardization process seems to strongly depend on intellectual property issues that might affect the LWE-based candidates. While the differences between NTRU and the other finalists are more obvious, it remains an important goal to evaluate the influence of the small but important differences between Kyber and Saber. The work of [BGR<sup>+</sup>21] and this work are the first ones that present a masked implementation of Kyber. Therefore, Kyber and Saber have never been directly compared from a protection perspective before. Moreover, it has been postulated that Saber is more efficient to mask [BDK<sup>+</sup>21] because the prime modulus in Kyber seems to complicate the introduction of countermeasures.

To provide a comparison in this regard, we propose a masked implementation of Kyber and Saber on a RISC-V microcontroller. At the same time, we propose the first hardware accelerators and ISA extensions for masking lattice-based cryptography. An open-source processor, e.g., a RISC-V core, is in many ways an ideal platform for masking. On one hand, we accelerate computational bottlenecks but keep the flexibility of software solutions. On the other hand, masking critical routines in open-sourced hardware gives us tight control over any side-channel leakage related to the microarchitecture of the processor [BGG<sup>+</sup>15].

In contrast to the non-masked ISA extensions for NewHope/Kyber/Saber in [FSS20] and NewHope/Kyber in [AEL<sup>+</sup>20], our HW/SW codesign provides accelerators for the bottlenecks of masked implementations, as well as more generic and powerful accelerators usable for a variety of schemes. In a masked implementation, many operations have to be duplicated, and performance bottlenecks become more evident. Although the polynomial multiplication was already thoroughly studied, to the best of our knowledge, a generic multiplier covering a wide range of schemes is still missing. Prior works analyzed the usage of the Number Theoretic Transform (NTT) for schemes that originally use other multiplication methods [FSS20, CHK<sup>+</sup>21], but an efficient hardware solution is still missing.

Our specific contributions can be summarized as follows.

#### Generic accelerators and instruction set extensions. We provide:

- A generic NTT-based hardware multiplier suitable for a variety of lattice-based PKE/KEM and signature schemes supporting positive/negative wrapped convolutions, incomplete NTTs, and prime lifts;

- New cycle count records for Saber and Kyber on a RISC-V platform with ISA extensions and hardware accelerators.

#### Masked accelerators. We provide:

- A novel algorithm for masked compression with prime moduli;

- Masked hardware accelerators for hashing, binomial sampling, A2B/B2A conversions, and compression;

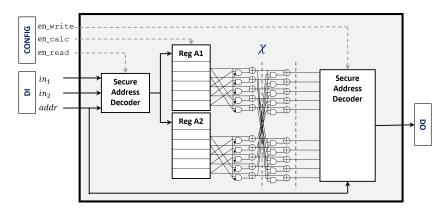

- Measures towards secure system design with share separation;

- The first masked HW/SW codesigns for PQC with Saber and Kyber as case study (one of the first masked Kyber implementation in general).

The implementation of this work is publicly available at https://gitlab.lrz.de/ tueisec/masked-post-quantum-crypto.

**Paper organization.** Section 1 provides an overview about mathematical hard problems used to construct lattice-based cryptography, the theoretical background of masking as one of the main countermeasures against SCA, and the decapsulation operation of the PQC finalists Kyber and Saber. Section 2 presents how the masking method can be applied for Kyber and Saber. In Sections 3 and 4, hardware accelerators for the linear and non-linear operations are presented. The system integration of these accelerators is described in Section 5. The experimental results of the leakage assessment of our accelerators and the performance evaluation for Kyber and Saber are given in Section 6. The work is summarized in Section 7.

## 1 Preliminaries

## 1.1 Module Learning With Errors and Module Learning with Rounding

The NIST PQC finalists Kyber and Saber are based on the Module Learning with Errors (MLWE) and Module Learning with Rounding (MLWR) problems, respectively. The MLWE and MLWR problems are both variants of the Ring Learning with Errors (RLWE) problem [LPR10].

Let  $\lfloor x \rfloor$  denote the flooring operation, i.e. rounding towards negative infinity. The rounding operation  $\lfloor x \rceil$  rounds towards the nearest integer with ties being rounded up,

in other words, it holds that  $\lfloor x \rceil = \lfloor x + 0.5 \rfloor$ . We also reserve the notations  $\lfloor x \rfloor_f$  and  $\lfloor x \rceil_f$  which implies flooring (resp. rounding) x up to f fractional digits. We reserve bold notation for matrices and vectors (of polynomials).

Let  $\mathcal{R}_q = \mathbb{Z}_q/\langle \phi(x) \rangle$  be a polynomial ring with the integer q and the cyclotomic polynomial  $\phi(x)$ . An MLWE instance is defined by  $(\mathbf{A}, \mathbf{b} = \mathbf{A} \cdot \mathbf{s} + \mathbf{e})$  with the public matrix  $\mathbf{A} \in \mathcal{R}_q^{k_1 \times k_2}$  sampled from a uniform distribution  $\mathcal{U}$ , the secret  $\mathbf{s} \in \mathcal{R}_q^{k_2}$  sampled from a binomial distribution  $\Psi_{\eta_1}$  with parameter  $\eta_1$ , and the error  $\mathbf{e} \in \mathcal{R}_q^{k_1}$  sampled from  $\Psi_{\eta_2}$  with parameter  $\eta_2$ . In contrast, the MLWR instance is defined by  $(\mathbf{A}, \mathbf{b} = \lfloor \frac{p}{q}(\mathbf{A} \cdot \mathbf{s}) \rfloor)$ , replacing the error by a deterministic rounding function that scales the product by p/q and rounds the result to the nearest integer modulo p. As it is known to be a hard problem to distinguish MLWE/MLWR samples from a uniform sample pair and to recover the secret from  $\mathbf{b}$ , these samples are well suited to build cryptographic schemes.

## 1.2 Accelerator Types

Hardware accelerators for computationally intensive tasks can be used to improve the overall performance of PQC implementations. Such accelerators can be divided into two categories.

**Loosely coupled accelerators.** This type of accelerator is placed outside of the main processor. The design is usually independent of the processor and thus allows a good portability. The accelerator can be connected via a bus system. Due to the high bus communication overhead, loosely coupled accelerators are mostly suitable for large and computationally intensive tasks with a low interaction between processor and accelerator.

**Tightly coupled accelerators.** This type of accelerator is directly integrated into the main processor and can be accessed using ISA extensions. The advantages are that no complex bus communication is required to access data from the register files. Usually, these kinds of accelerators are much smaller compared to loosely coupled accelerators. This does not only decrease the area requirements but can also lead to a high flexibility.

## 1.3 Masking

Masking [CJRR99] is a well-known countermeasure against SCA. It splits a secret variable into multiple parts called shares. A first-order masking uses two shares, and aims to protect against SCA that extract information from the first-order statistical moment. The algorithm is executed on these shares individually to hide any power consumption that would be correlated with the original secret.

As we deal with matrices and vectors of polynomials, which are further split into shares, we use several separate indices. To index a matrix or a vector, we use square brackets, e.g.  $\mathbf{A}[i][j]$ . We use a subscript, e.g.  $\mathbf{b}[0]_i$ , to access the *i*-th coefficient of the polynomial  $\mathbf{b}[0]$  (or also the *i*-th bit of a variable depending on the context). Finally, we reserve a superscript, e.g.  $\mathbf{b}[0]^i$ , to access the *i*-th share of  $\mathbf{b}[0]$ . In algorithms and figures, we highlight shared variables with *s* shares, by explicitly writing them as  $\mathbf{b}^{\{0:s-1\}}$ .

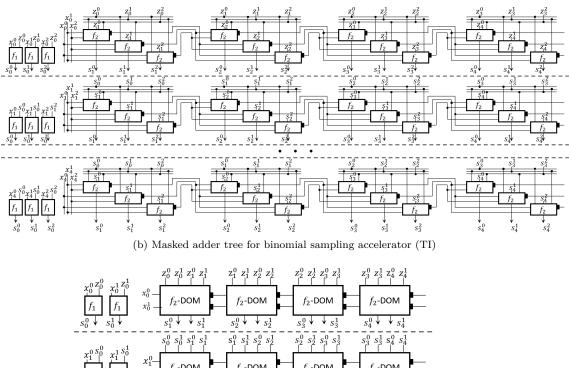

**Threshold Implementations (TI).** TI is an effective method to prevent SCA and leakages caused by glitches [NRR06]. The concept is based on multi-party computations. For a TI the following properties must hold: correctness (the result after the computations remains correct), non-completeness (the partial functions and computations are at least independent of one input share), and uniformity (input and output are uniformly distributed). For a security order of d and a function of algebraic degree t, the number of input shares must be  $s \ge td + 1$ . Thus, first-order TIs require a minimum of three input shares for non-linear functions.

**Domain Oriented Masking (DOM).** DOM is another masking method that provides side-channel resistance and glitch protection [GMK16]. In contrast to the function-oriented nature of TI, DOM operates on share domains. Operations that process shares from a single domain are uncritical as they can only leak information from one particular share domain. Without the information of the remaining domains, an attacker gains no advantage. Non-linear operations that combine shares from different domains require additional randomness to refresh the cross-domain operations. Registers in the cross-domain paths make sure that the terms are refreshed before being combined to the resulting shares and thus, prevent glitches. The first-order DOM representation of an *AND*-gate is an important example for DOM [GMK16].

#### 1.4 Horizontal Attacks on Masked Implementations

The aim of this work is to present novel masked accelerators and to compare Saber and Kyber from a masking perspective. The algorithms outlined in Section 2 aim to protect our implementation against first-order DPA. Apart from the implemented masked equality test, these components extend readily to higher-order masking, which secures against higher-order DPA.

Besides DPA, other side-channel attack vectors must be considered as well. In particular, there is a broad category of attacks that analyze side-channel traces *horizontally*. These attacks are able to defeat masking countermeasures as the leakage of both corresponding shares is already present in a single horizontal trace. Single-trace template attacks against masked NTT software implementations have been shown in [PPM17, PP19] and against Keccak in [KPP20]. The attacks of these works are based on Soft-Analytical Side-Channel Attacks (SASCA) [VCGS14], which take the output of a template attack and feed it into a graph representation to apply belief propagation. This method allows to retrieve correct results, although a single trace is usually not sufficient due to, e.g., a low SNR measurement. In contrast to the previously described attacks, where shares are retrieved independently, [NDGJ21] uses a deep-learning model to directly combine leakage of the individual shares horizontally. They show an attack on the masked Saber implementation of [BDK<sup>+</sup>21], recovering the secret key in as few as 16 traces.

Increasing the masking order provides only limited extra security against these types of attacks, since each share is still present horizontally in the trace. Effective countermeasures against such attacks are hiding techniques, especially shuffling, as they break the temporal localization of leakage within a trace. As these countermeasures are usually less expensive than masking and can be implemented similarly for Kyber and Saber, we leave their evaluation for future work. An evaluation of such hiding countermeasures for R-LWE schemes was conducted in [OSPG18]. The authors reported 1% overhead on top of the masked design. In [RPBC20] the authors evaluate different possibilities of shuffling for the NTT as a countermeasure against single-trace attacks and reported an overhead in the range of 181% up to 356% in comparison to an unprotected NTT software implementation.

Hiding is an interesting field of research for an open-source platform like RISC-V because countermeasures can be integrated in hardware (within a dedicated accelerator) or in software. Hardware implementations have the advantage that multiple shares can be processed simultaneously. This way, the trace can no longer be partitioned into each of the shares. Additionally, in both software or hardware, shuffling countermeasures can be extended with blinding techniques [Saa18, ZBT19, HP21] to further increase the noise levels. In our design, the integration of hiding techniques might require further pre- and post-processing steps and hardware modifications, e.g., changes in address units. A detailed analysis of the integration of hiding techniques is outside the scope of this work.

| Algorithm 1: SABER.CPA.DEC.                                                           | Algorithm 2: Kyber.CPA.Dec.                                             |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Input: Secret key s                                                                   | Input: Secret key s                                                     |

| <b>Output:</b> Message $m$                                                            | <b>Output:</b> Message $m$                                              |

| 1 $\mathbf{u} \leftarrow \mathbf{c}_1$                                                | 1 $\mathbf{u} \leftarrow \texttt{Decompress}_q(\mathbf{c}_1, d_u)$      |

| 2 $v \leftarrow h_2 - 2^{\epsilon_p - \epsilon_T} \cdot c_2$                          | 2 $v \leftarrow \texttt{Decompress}_q(c_2, d_v)$                        |

| $\mathbf{s} \ m = (v + (\mathbf{s} \bmod p) \cdot \mathbf{u}^T) \gg (\epsilon_p - 1)$ | 3 $m = \texttt{Compress}_q(\hat{v} - \mathbf{s} \cdot \mathbf{u}^T, 1)$ |

| Algorithm 3:                                                                          | Algorithm 4:                                                                                                                 |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| SABER.CPA.ENC.                                                                        | Kyber.CPA.Enc.                                                                                                               |

| <b>Input:</b> Public key $pk = (seed_A, \mathbf{b})$                                  | <b>Input:</b> Public key $pk = (seed_A, \mathbf{b})$                                                                         |

| Input: Message $m$                                                                    | Input: Message $m$                                                                                                           |

| Input: Seed $r$                                                                       | Input: Seed $r$                                                                                                              |

| <b>Output:</b> Ciphertext $\mathbf{c} = (\mathbf{c_1}, c_2)$                          | <b>Output:</b> Ciphertext $\mathbf{c} = (\mathbf{c_1}, c_2)$                                                                 |

| 1 $\mathbf{A} \stackrel{seed_A}{\leftarrow} \mathcal{U}(\mathcal{R}_q^{k 	imes k})$   | 1 $\mathbf{A} \stackrel{seed_A}{\leftarrow} \mathcal{U}(\mathcal{R}_q^{k \times k})$                                         |

| $2 \mathbf{s}' \stackrel{XOF(r)}{\leftarrow} \Psi_{\eta}$                             | $2 \ (\mathbf{s}', \mathbf{e}_1, e_2) \stackrel{XOF(r)}{\leftarrow} \Psi_{\eta_1} \times \Psi_{\eta_2} \times \Psi_{\eta_2}$ |

| $3 \ \mathbf{u} \leftarrow \mathbf{A} \cdot \mathbf{s}'$                              | $\mathbf{a} \ \mathbf{u} \leftarrow \mathbf{A} \cdot \mathbf{s}' + \mathbf{e}_1$                                             |

| 4 $v \leftarrow \mathbf{b}^T \cdot (\mathbf{s}' \mod p) - 2^{\epsilon_p - 1} \cdot m$ | 4 $v \leftarrow \mathbf{b}^T \cdot \mathbf{s}' + e_2 + \left\lceil \frac{q}{2} \right\rfloor \cdot m$                        |

| 5 $\mathbf{c}_1 \leftarrow (\mathbf{u} + \mathbf{h}) \gg (\epsilon_q - \epsilon_p)$   | 5 $\mathbf{c}_1 \leftarrow \texttt{Compress}_q(\mathbf{u}, 	ilde{d}_u)$                                                      |

| $6 \ c_2 \leftarrow (v+h_1) \gg (\epsilon_p - \epsilon_T)$                            | 6 $c_2 \leftarrow \texttt{Compress}_q(v, d_v)$                                                                               |

## 1.5 Kyber and Saber Decapsulation

Both Kyber and Saber include a CPA-secure encryption scheme, from which they build a CCA-secure KEM. Since the plain encryption scheme can be already broken without DPA using CCA-style attacks, we choose to mask the CCA-secure KEM. Moreover, DPA typically requires a large amount of collected traces to be effective. The CCA-secure decapsulation is the only feasible target, since this constitutes the only operation where multiple traces can be collected for the same long-term secret key. As such, we focus our masking efforts on the decapsulation of Kyber and Saber.

In some scenarios, key generation or encapsulation might also need to be protected against SCA. However, in that case, the adversary usually has access to only a single trace to either retrieve the long-term secret key or the ephemeral session key, respectively. Attacks that target these operations therefore typically fall into the category of horizontal attacks. As mentioned before, we leave a detailed treatment of hiding techniques, and consequently secure implementations of key generation and encapsulation, as future work. Masking techniques cannot fully protect against the horizontal type of attacks, but they can still be used to harden the implementation. Both key generation and encapsulation require the same primitive operations as decapsulation, and our masking techniques would be equally applicable for these routines.

In Algorithms 1–6, we recall the decapsulation of Kyber and Saber, which uses the CPA-secure encryption and decryption as subroutines. We use a simplified notation that highlights both the similarities and differences between the two schemes. The listings use common symbols and operators, they hide the encodings into byte arrays, and they abstract away from the various transformations into and out of NTT domain. We note that Kyber uses a prime modulus q = 3329, whereas Saber chooses power-of-two moduli  $q = 2^{13}$  and  $p = 2^{10}$ . For a full description of Kyber and Saber, we refer to their respective round 3 specification documents [SAB+20, DKR+20]. Both Kyber and Saber use a variety of symmetric primitives, all of which are based on the SHA3 standard: the hash functions  $\mathcal{G}$  and  $\mathcal{H}$ , an extendable output functions XOF, and a key-derivation function KDF.

| Algorithm 5:                                                                           | Algorithm 6:                                                                           |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| SABER.CCAKEM.DECAPS.                                                                   | Kyber.CCAKEM.Decaps.                                                                   |

| Input: Ciphertext c                                                                    | Input: Ciphertext c                                                                    |

| <b>Input:</b> Secret key $\mathbf{sk} = (\mathbf{s}, \mathbf{pk}, \mathcal{H}(pk), z)$ | <b>Input:</b> Secret key $\mathbf{sk} = (\mathbf{s}, \mathbf{pk}, \mathcal{H}(pk), z)$ |

| Output: Key K                                                                          | Output: Key K                                                                          |

| 1 $m' := $ SABER.CPA.DEC $(\mathbf{s}, \mathbf{c})$                                    | 1 $m' := \text{Kyber.CPA.Dec}(\mathbf{s}, \mathbf{c})$                                 |

| 2 $(\bar{K}',r') := \mathcal{G}(m'  \mathcal{H}(pk))$                                  | 2 $(\bar{K}',r') := \mathcal{G}(m'  \mathcal{H}(pk))$                                  |

| <b>3</b> $\mathbf{c}' := \text{SABER.CPA.Enc}(\mathbf{pk}, m', r')$                    | <b>3</b> $\mathbf{c}' := \mathrm{KYBER.CPA.Enc}(\mathbf{pk}, m', r')$                  |

| 4 if $\mathbf{c} = \mathbf{c}'$ then                                                   | 4 if $\mathbf{c} = \mathbf{c}'$ then                                                   |

| 5 $K := KDF(\overline{K}'    \mathcal{H}(\mathbf{c}))$                                 | 5 $K := KDF(\bar{K}'  \mathcal{H}(\mathbf{c}))$                                        |

| 6 else                                                                                 | 6 else                                                                                 |

| $7     K := \mathrm{KDF}(z  \mathcal{H}(\mathbf{c}))$                                  | $7     K := \mathrm{KDF}(z  \mathcal{H}(\mathbf{c}))$                                  |

| s end                                                                                  | s end                                                                                  |

## 2 Masking Kyber and Saber

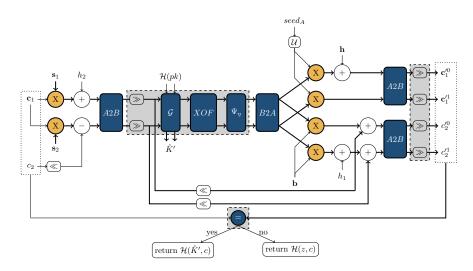

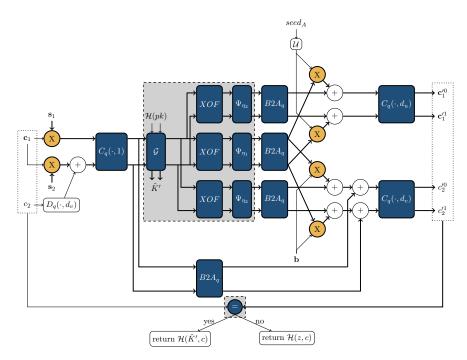

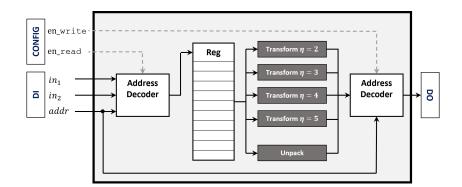

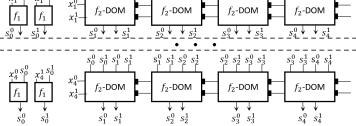

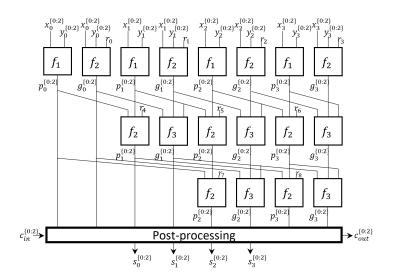

In this section, we describe the algorithms and methods necessary to create masked implementations of Kyber and Saber. These algorithms define the hardware architectures of our secure accelerators. Our masked implementations of the decapsulation operation in Saber and Kyber are illustrated in Figures 1 and 2, respectively.

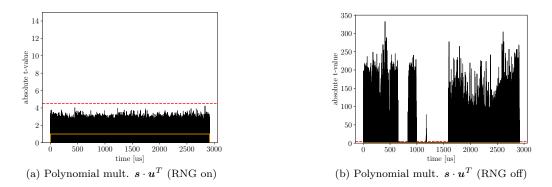

As MLWE/MLWR-based schemes, Saber and Kyber use polynomial arithmetic as their main computational building block. Linear operations, such as ring multiplications with an unmasked input, additions, and subtractions, can be duplicated and performed on each arithmetic share individually. As a result, expensive operations such as polynomial multiplications become increasingly attractive to accelerate in hardware. Our developed generic hardware accelerator for polynomial arithmetic is presented in Section 3. The polynomial multiplications that we accelerate are highlighted in yellow in Figures 1 and 2.

Non-linear operations are more complex to mask. These operations combine information from both of the shares, and special care must be taken such that they do not jointly leak the secret unmasked value. In Figures 1 and 2, these operations are highlighted in blue. Typically, these operations are expressed in terms of bit-operations, and it is often more natural to fall back to methods based on Boolean masking. The combination of both arithmetic and Boolean masking in Saber and Kyber requires the use of mask conversion algorithms to switch from either Boolean to Arithmetic (B2A) or Arithmetic to Boolean (A2B) masking.

A masked implementation of Saber decapsulation targeting the ARM Cortex-M4 has been proposed in  $[BDK^+21]$ . The authors of  $[BDK^+21]$  show that Saber is relatively efficient to mask, and argue that this is due to Saber's choice for a power-of-two modulus and the deterministic rounding of MLWR. For the non-linear masked routines, they use a masked Keccak implementation [BDPVA10], a masked binomial sampler [SPOG19], and a masked comparison algorithm [OSPG18], and these exact same methods can be reused for a masked implementation of Kyber. We integrate them into our secure masked accelerators and discuss their hardware architectures in Section 4. To implement B2A and A2B conversions, the authors of  $[BDK^+21]$  adopt an algorithm due to Goubin [Gou01] and a table-based algorithm [CT03], respectively. Both of these algorithms are specialized for power-of-two moduli and can therefore not directly be reused for Kyber. Motivated by this observation, we choose to implement different B2A and A2B conversions that we implement, and we subsequently use them to propose a novel method for masked ciphertext compression.

Figure 1: Masked decapsulation of Saber [BDK<sup>+</sup>21]. Linear performance bottlenecks highlighted in yellow, non-linear masked routines highlighted in blue, operations that require Boolean masking grouped in light grey.

Figure 2: Masked decapsulation of Kyber. Linear performance bottlenecks highlighted in yellow, non-linear masked routines highlighted in blue, operations that require Boolean masking grouped in light grey.

## 2.1 B2A and A2B Conversions

B2A and A2B conversions allow to securely convert between an arithmetic masking  $x = A^0 + A^1$  and a Boolean masking  $x = B^0 \oplus B^1$ . These methods may choose to keep a single random mask  $A^1 = B^1 = R$ , in which case the conversions compute either

$$B^{0} = (A^{0} + R) \oplus R$$

, or  $A^{0} = (B^{0} \oplus R) - R$

without unmasking x.

A2B and B2A conversion methods were first proposed by Goubin [Gou01]. In software implementations, A2B conversions can efficiently be implemented using table-based methods [CT03, Deb12, VBDV21]. This is the approach taken in [OSPG18] and [BDK<sup>+</sup>21]. The drawbacks of table-based methods are that they do not extend to higher-order security, require work-arounds to handle prime moduli [OSPG18], and that they are relatively difficult to translate to a hardware implementation that also resists glitches. B2A conversions, on the other hand, are typically not table-based. In [BDK<sup>+</sup>21], Goubin's B2A method is used, which is specialized for power-of-two moduli. Some ad-hoc methods for prime-modulus B2A<sub>q</sub> and A2B<sub>q</sub> conversion were proposed in [OSPG18], and subsequently formalized in [BBE<sup>+</sup>18] and [SPOG19].

In contrast to the previous masked implementations [OSPG18] and [BDK<sup>+</sup>21], we employ A2B and B2A conversions that are based on secure masked arithmetic addition over Boolean shares (SecAdd) [CGV14]. Our reasoning is many-fold. First, since both A2B and B2A conversion can be expressed in terms of SecAdd, we are able to accelerate both operations with a single hardware block. Second, in [BBE<sup>+</sup>18] this secure adder was extended to work with prime moduli. SecAdd<sub>q</sub> essentially makes two calls to SecAdd, such that B2A<sub>q</sub> and A2B<sub>q</sub> can additionally be accelerated with the same SecAdd hardware. Third, SecAdd only requires the masked implementation of a binary adder, and efficient TI implementations of ripple-carry or Kogge-Stone variants have already been proposed [SMG15]. Finally, the A2B and B2A approaches based on secure addition are readily extensible to higher-order security, which is not the case for table-based A2B or Goubin's B2A algorithms. We now describe the conversion based on SecAdd in detail. Our focus is on univariate, first-order side-channel security, and wherever possible we simplify the algorithms to focus on this case. For a general description focusing on arbitrary orders and (multivariate) composability, we refer to the original works [CGV14, BBE<sup>+</sup>18].

**SecAdd** takes as inputs the Boolean maskings  $\mathbf{x}^{\{0:1\}} = (x^0, x^1)$  and  $\mathbf{y}^{\{0:1\}} = (y^0, y^1)$  and outputs a Boolean masking  $\mathbf{s}^{\{0:1\}} = (s^0, s^1)$  such that  $(s^0 \oplus s^1) = (x^0 \oplus x^1) + (y^0 \oplus y^1)$ . **SecAdd**<sub>q</sub> [BBE<sup>+</sup>18] can be constructed from **SecAdd** by securely computing a second sum  $(s'^0 \oplus s'^1) = (s^0 \oplus s^1) + (q'^0 \oplus q'^1)$ , where  $(q'^0, q'^1)$  is a Boolean masking of -q in two's complement form. If  $x + y \ge q$ , then s' = (x + y - q) is the correct sum  $(x + y) \mod q$ , and it also holds that  $s' \ge 0$ . Alternatively, if x + y < q, then s = (x + y) is the correct sum and s' < 0. Since s' is negative in one case and positive in the other, the masked sign bit  $c = \operatorname{sign}(s')$  can be used to select the correct sum:

$$\mathtt{SecMux}(\mathbf{s}^{\{0:1\}}, \mathbf{s'}^{\{0:1\}}, \mathbf{c}^{\{0:1\}}) = \mathtt{SecAnd}((\mathbf{c}\|...\|\mathbf{c})^{\{0:1\}}, \mathbf{s}^{\{0:1\}}) \oplus \mathtt{SecAnd}(\neg(\mathbf{c}\|...\|\mathbf{c})^{\{0:1\}}, \mathbf{s'}^{\{0:1\}}).$$

Having a distinct sign bit requires that s' is computed up to at least  $w = \lceil \log_2(q) \rceil + 1$  bits, i.e. one bit larger than the initial masks. SecAdd<sub>q</sub> is illustrated in Algorithm 7.

We propose a new simplified version of  $\text{SecAdd}_q$ , which assumes that the input shares already satisfy  $(x^0 \oplus x^1) + (y^0 \oplus y^1) = x + y - q$  in two's complement<sup>1</sup>. In this case, it is possible to directly compute s' = x + y - q through  $\text{SecAdd}(\mathbf{x}^{\{0:1\}}, \mathbf{y}^{\{0:1\}})$ . If s' < 0, q

$<sup>^{1}</sup>$ In what follows, we'll see that this is easily possible for the A2B and B2A conversions based on SecAdd.

| Algorithm 7: SecAdd <sub>q</sub> [BBE <sup>+18]</sup>                                                                                          | Algorithm 8: SecAdd $_q$ simplified                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Input: $\mathbf{x}^{\{0:1\}} = (x^0, x^1), \mathbf{y}^{\{0:1\}} = (y^0, y^1)$                                                                  | <b>Input:</b> $\mathbf{x}^{\{0:1\}} = (x^0, x^1), \mathbf{y}^{\{0:1\}} = (y^0, y^1)$                   |

| such that $x = x^0 \oplus x^1$ , $y = y^0 \oplus y^1$                                                                                          | such that                                                                                              |

| <b>Result:</b> $\mathbf{z}^{\{0:1\}} = (z^0, z^1)$ such that                                                                                   | $x + y + (2^w - q) = (x^0 \oplus x^1) + (y^0 \oplus y^1)$                                              |

| $z = z^0 \oplus z^1 = x + y \bmod q$                                                                                                           | <b>Result:</b> $\mathbf{z}^{\{0:1\}} = (z^0, z^1)$ such that                                           |

| $1 \ \mathbf{q}^{\prime \{0:1\}} \leftarrow (2^w - q, 0)$                                                                                      | $z = z^0 \oplus z^1 = x + y \mod q$                                                                    |

| $2 \hspace{0.1 in} \mathbf{s}^{\{0:1\}} \hspace{0.1 in} \leftarrow \mathtt{SecAdd}(\mathbf{x}^{\{0:1\}}, \mathbf{y}^{\{0:1\}})$                | $1 \mathbf{s}^{\prime \{0:1\}} \leftarrow \texttt{SecAdd}(\mathbf{x}^{\{0:1\}}, \mathbf{y}^{\{0:1\}})$ |

| $3 \hspace{0.1in} \mathbf{s'}^{\{0:1\}} \hspace{0.1in} \leftarrow \hspace{0.1in} \mathtt{SecAdd}(\mathbf{s}^{\{0:1\}}, \mathbf{q'}^{\{0:1\}})$ | <b>2</b> $\mathbf{c}^{\{0:1\}} \leftarrow (\mathbf{s}'^{\{0:1\}} \gg (w-1))$                           |

| 4 $\mathbf{c}^{\{0:1\}} \leftarrow (\mathbf{s}^{\{0:1\}} \gg (w-1))$                                                                           | $\mathbf{s}  \mathbf{c}^{\prime\{0:1\}} \leftarrow (c^0 \cdot q, c^1 \cdot q)$                         |

| $\texttt{5} \ \mathbf{z}^{\{0:1\}} \ \leftarrow \texttt{SecMux}(\mathbf{s}^{\{0:1\}}, \mathbf{s'}^{\{0:1\}}, \mathbf{c}^{\{0:1\}})$            | 4 $\mathbf{z}^{\{0:1\}} \leftarrow \texttt{SecAdd}(\mathbf{s}'^{\{0:1\}}, \mathbf{c}'^{\{0:1\}})$      |

| Algorithm 9: A2B [CGV14]                                                                                           | Algorithm 10: $A2B_q$ [BBE <sup>+</sup> 18]                                                           |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| <b>Input:</b> $\mathbf{x}^{\{0:1\}} = (A^0, A^1)$ such that                                                        | <b>Input:</b> $\mathbf{x}^{\{0:1\}} = (A^0, A^1)$ such that                                           |

| $x = A^0 + A^1 \mod 2^k$                                                                                           | $x = A^0 + A^1 \mod q$                                                                                |

| <b>Result:</b> $\mathbf{x}^{\{0:1\}} = (B^0, B^1)$ such that                                                       | <b>Result:</b> $\mathbf{x}^{\{0:1\}} = (B^0, B^1)$ such that                                          |

| $x = B^0 \oplus B^1$                                                                                               | $x = B^0 \oplus B^1$                                                                                  |

| 1 $R^0, R^1 \stackrel{\$}{\leftarrow} \mathbb{Z}_{2^k}$                                                            | 1 $R^0, R^1 \stackrel{\$}{\leftarrow} \mathbb{Z}_q$                                                   |

| <b>2</b> $\mathbf{B}_{1}^{\{0:1\}} \leftarrow (A^{0} \oplus R^{0}, R^{0})$                                         | <b>2</b> $\mathbf{B}_{1}^{\{0:1\}} \leftarrow (A^{0} \oplus R^{0}, R^{0})$                            |

| <b>3</b> $\mathbf{B}_{2}^{\{0:1\}} \leftarrow (A^{1} \oplus R^{1}, R^{1})$                                         | <b>3</b> $\mathbf{B}_{2}^{\{0:1\}} \leftarrow ((A^{1} + (2^{w} - q)) \oplus R^{1}, R^{1})$            |

| $4 \hspace{0.1in} \mathbf{x}^{\{0:1\}} \leftarrow \texttt{SecAdd}(\mathbf{B}_1^{\{0:1\}}, \mathbf{B}_2^{\{0:1\}})$ | 4 $\mathbf{x}^{\{0:1\}} \leftarrow \texttt{SecAdd}_q(\mathbf{B}_1^{\{0:1\}}, \mathbf{B}_2^{\{0:1\}})$ |

must be added again to find the correct sum. This time, rather than using  $c = \operatorname{sign}(s')$  to multiplex between s' and s' + q, we compute the correct sum as  $s = s' + c \cdot q$ . This is easily possible, since the multiplication with q distributes over the masking  $c^0 \oplus c^1 = c$ , i.e.  $q \cdot c^0 \oplus q \cdot c^1 = q \cdot c$ . Our simplified SecAdd<sub>q</sub> routine is shown in Algorithm 8. It avoids the masked multiplexer altogether.

**A2B** conversion follows directly from SecAdd. Given an arithmetic masking  $x = A^0 + A^1$ , the secure addition of  $A^0$  and  $A^1$  with outputs in Boolean masked form is exactly an A2B conversion. A2B and A2B<sub>q</sub> based on this idea are illustrated in Algorithms 9 and 10. In these algorithms, the shares  $A^0$  and  $A^1$  are first themselves shared as a Boolean masking, before being fed into SecAdd. As we hinted at before, we have full control over this initial Boolean masking. Therefore, for A2B<sub>q</sub>, we create an initial masking of  $A^0 + A^1 - q$ , and use our simplified version of SecAdd<sub>q</sub>.

**B2A** conversion uses a similar idea. Given a Boolean masking  $x = B^0 \oplus B^1$ , the first arithmetic share  $A^0$  is simply sampled randomly. The second arithmetic share can then be computed from the first one by securely computing  $A^1 = (B^0 \oplus B^1) - A^0 \mod 2^k$ . Like in the A2B case, first a Boolean masking is created of  $-A^0 \mod 2^k$  and subsequently this is fed into SecAdd. The result is a Boolean masking  $A^1 = B^0 \oplus B^1$ , which can be decoded<sup>2</sup> to find the second share  $A^1$ . B2A and B2A<sub>q</sub> are illustrated in Algorithms 11 and 12. Again, to utilize our simplified and more efficient version of SecAdd<sub>q</sub>, we simply create an initial two's complement Boolean sharing of  $(-A^0 \mod q) - q$  instead.

## 2.2 Masked Compression

Both Saber and Kyber include a compression operation that rounds away some low-order bits of a ring element. In Line 3 of the decryption step, the compression operation is used for message decoding, i.e. mapping  $\left(\left\lceil \frac{q}{2} \right\rfloor \cdot m + e\right)$  back to m. In the encryption step, Lines 5 and 6, the same operation is used to compress the ciphertext components  $\boldsymbol{u}$  and  $\boldsymbol{v}$ .

<sup>&</sup>lt;sup>2</sup>This requires a secure FullXor(B) for composability proofs [CGV14].

| Algorithm 11: B2A [CGV14]                                                                                     | Algorithm 12: $B2A_q$ [BBE <sup>+</sup> 18]                                                                            |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| <b>Input:</b> $\mathbf{x}^{\{0:1\}} = (B^0, B^1)$ such that                                                   | <b>Input:</b> $\mathbf{x}^{\{0:1\}} = (B^0, B^1)$ such that                                                            |

| $x = B^0 \oplus B^1$                                                                                          | $x = B^0 \oplus B^1$                                                                                                   |

| <b>Result:</b> $\mathbf{x}^{\{0:1\}} = (A^0, A^1)$ such that                                                  | <b>Result:</b> $\mathbf{x}^{\{0:1\}} = (A^0, A^1)$ such that                                                           |

| $x = A^0 + A^1 \mod 2^k$                                                                                      | $x = A^0 + A^1 \mod q$                                                                                                 |

| 1 $A^0, R \stackrel{\$}{\leftarrow} \mathbb{Z}_{2^k}$                                                         | 1 $A^0, R \stackrel{\$}{\leftarrow} \mathbb{Z}_q \times \mathbb{Z}_{2^w}$                                              |

| <b>2</b> $\mathbf{B}_{1}^{\{0:1\}} \leftarrow ((2^{k} - A^{0}) \oplus R, R)$                                  | <b>2</b> $\mathbf{B}_1^{\{0:1\}} \leftarrow (((q - A^0) + (2^w - q)) \oplus R, R)$                                     |

| $3 \hspace{0.1cm} \mathbf{B}_2^{\{0:1\}} \gets \texttt{SecAdd}(\mathbf{x}^{\{0:1\}}, \mathbf{B}_1^{\{0:1\}})$ | $3 \hspace{0.1 cm} \mathbf{B}_{2}^{\{0:1\}} \gets \texttt{SecAdd}_{q}(\mathbf{x}^{\{0:1\}}, \mathbf{B}_{1}^{\{0:1\}})$ |

| 4 $\mathbf{x}^{\{0:1\}} \leftarrow (A^0, B^0_2 \oplus B^1_2)$                                                 | <b>4</b> $\mathbf{x}^{\{0:1\}} \leftarrow (A^0, B_2^0 \oplus B_2^1)$                                                   |

For Saber, ciphertext compression is inherently tied to the security of its MLWR instance, whereas Kyber initially<sup>3</sup> only compressed the ciphertext components to reduce their size.

The Kyber compression function takes an input  $x \in \mathbb{Z}_q$  and outputs an integer in  $\{0, \ldots, 2^d - 1\}$ , where  $d < \lceil \log_2(q) \rceil$ :

$$\operatorname{Compress}_q(x,d) = \lceil (2^d/q) \cdot x \rfloor \mod 2^d \tag{1}$$

For Saber, where  $q = 2^{13}$  is a power of two,  $Compress_{2^k}$  can be expressed as a more simple logical shift. In order to round the result instead of flooring, the constant  $h_1, h_2$  or **h** are added before the shift.

Compression must discard some lower-order bits of arithmetically masked ring elements. Discarding these bits is inherently a Boolean operation, and A2B conversion can help to mask this operation effectively. In [BDK<sup>+</sup>21], a new technique is proposed to optimize A2B conversion for masked logical shifting in Saber. Compression for prime moduli has so far only been treated in the context of message decoding in [RRVV15] and [OSPG18]. We first review these existing approaches and show that they do not extend efficiently to ciphertext compression. Subsequently, we outline a novel method to mask Compress<sub>q</sub>, which is simple and efficient to implement.

#### 2.2.1 MaskedCompress<sub>2k</sub>

For power-of-two moduli, ciphertext compression constitutes a simple rounded logical shift. In an arithmetic sharing,  $(x_{msb} || x_{lsb}) = (A^0_{msb} || A^0_{lsb}) + (A^1_{msb} || A^1_{lsb})$ , this shift needs special consideration because the lower bits  $A^0_{lsb} + A^1_{lsb}$  might contain a carry that must be added to the upper bits before they are shifted out. A straightforward solution is to first perform A2B conversion, since a Boolean masking  $(x_{msb} || x_{lsb}) = (B^0_{msb} || B^0_{lsb}) \oplus (B^1_{msb} || B^1_{lsb})$  does not have any carries.

The masked Saber implementation of  $[BDK^+21]$  optimizes table-based A2B conversion to only compute the carry for the lower bits, rather than a full conversion. This carry is subsequently added to the higher bits, leaving them as an arithmetic sharing. The full procedure is termed A2A conversion.

The A2A optimization also applies to the A2B conversion based on SecAdd. In this setting, when only the carry-out is required, all the summation logic can be pruned from the binary adder. Furthermore, since the carry is only needed at the final position, any carry look-ahead logic can be implemented maximally sparse. However, this optimization would also prevent us from supporting B2A conversion with the same SecAdd hardware. Hence, we implement the more simple solution, i.e. a full A2B conversion and subsequent share-wise logical shift.

$<sup>^3</sup>$ Since round 3, Kyber-512 relies to a small extent on the rounding noise to add security as well.

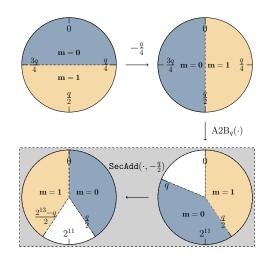

Figure 3: MaskedDecode<sub>q</sub>. The final result is a Boolean masking where the most significant bit is a masking  $(m^0 \oplus m^1) = m$ . Adapted from [OSPG18] to use A2B<sub>q</sub> instead of TransformPower2. Operations that require Boolean masking grouped in light gray.

#### 2.2.2 MaskedDecode<sub>q</sub>

Masked decoders have been proposed in [RRVV15] and [OSPG18]. Rather than dividing by the modulus, the decoding step is expressed as an interval comparison:

$$\mathsf{Decode}_q(m) = \mathsf{Compress}_q(m, 1) = \begin{cases} 0 \text{ for } m \in [\lceil 3q/4 \rceil, \lfloor q/4 \rfloor] \\ 1 \text{ for } m \in [\lceil q/4 \rceil, \lfloor 3q/4 \rfloor] \end{cases}$$

(2)

For an arithmetic masking  $x = A^0 + A^1$ , [RRVV15] proposes a probabilistic decoder that uses information on the quadrants of  $A^0$  and  $A^1$  in a masked table lookup. A different approach is taken in [OSPG18], where a series of A2B-related transformations are used to create a masked decoder. Lacking an existing  $A2B_q$  transform, the authors propose another conversion, **TransformPower2**, that transforms an arithmetic masking mod q to a masking mod  $2^k$ . Nevertheless, we do have an  $A2B_q$  conversion available, and use it to simplify the masked decoder of [OSPG18]. The resulting process is shown in Figure 3. The final result is a Boolean masking where the most significant bit is a masking of the decoded result:  $(m^0 \oplus m^1) = m$ .

#### 2.2.3 MaskedCompress<sub>q</sub>

Unfortunately, the techniques of masked decoding do not extend to masked compression. When dealing with 2 intervals of width  $\frac{q}{2}$ , it is possible to position their boundary exactly at a power of two as in Figure 3. However, already for d = 2 we have 4 intervals of width  $\frac{q}{d}$ , and this technique is no longer applicable.

We propose a substantially different masked compression technique. Rather than expressing it as an interval comparison, we analyze and mask the required division by the modulus q. The key idea is simple. First, we observe that the compression tolerates an approximate quotient  $x' \approx (2^d/q) \cdot x$ . In other words,

$$\mathsf{Compress}_a(x,d) = \lceil (2^d/q) \cdot x + e \mid \mod 2^d , \tag{3}$$

remains correct for a small bounded error e. The reason for this is apparent if we express  $(2^d/q) \cdot x$  as a binary fraction:

$$(2^d/q) \cdot x = \overbrace{(1)}^{\lfloor \frac{2^d \cdot x}{q} \rfloor} \bullet \overbrace{(1)}^{\frac{2^d \cdot x \mod q}{q}} \bullet (4)$$

The fractional part equals  $\frac{2^d \cdot x \mod q}{q}$ , and it is strictly limited to the set of values  $\frac{\{0, \dots, q-1\}}{q}$ . This fractional part is never exactly 0.5, but instead the edge-case values are  $\frac{\lfloor \frac{q}{2} \rfloor}{q} = \frac{1664}{3329}$  and  $\frac{\lceil \frac{q}{2} \rceil}{q} = \frac{1665}{3329}$ , which should be rounded down and up, respectively. These values are still rounded correctly, even when subject to a small error  $-\frac{1}{2q} \leq e < \frac{1}{2q}$ :

$$\lceil \frac{\lfloor \frac{q}{2} \rfloor}{q} + e \rfloor = 0 \tag{5}$$

$$\lceil \frac{\lceil \frac{q}{2} \rceil}{q} + e \rfloor = 1 \quad . \tag{6}$$

As a result, the approximate quotient  $\lceil (2^d/q) \cdot x + e \rfloor$  is rounded correctly, given the same bound on e.

Our simple but crucial observation to build  $MaskedCompress_q$  is that we can compute such an approximate quotient individually from the shares of  $x = x^0 + x^1 \mod q$ , using only finite-precision arithmetic. For example, using integer division, we can compute

$$\lfloor (2^d/q) \cdot x^0 \rfloor_f + \lfloor (2^d/q) \cdot x^1 \rfloor_f = ((2^d/q) \cdot x + e) \mod 2^d , \qquad (7)$$

which is a strict underestimate of the real quotient  $(2^d/q) \cdot x \mod 2^d$  with e < 0. More generally, we can compute rounded share-wise quotients,

$$\lfloor (2^d/q) \cdot x^0 \rceil_f + \lfloor (2^d/q) \cdot x^1 \rceil_f = ((2^d/q) \cdot x + e) \mod 2^d , \qquad (8)$$

with a bounded error e. In both cases, the rounding error e can be arbitrarily lowered by increasing the number of fractional bits f. As a result, for an appropriately large choice of f that fixes  $-\frac{1}{2q} \leq e < \frac{1}{2q}$ , the share-wise 'fixed-point' quotients of Equations 7 and 8 can be used to correctly retrieve the output of  $Compress_q$ .

We now analyze the requirements on f in detail. The share-wise quotients of Equations 7 and 8 consist of d integer and f fractional bits, with the remaining bits being truncated or rounded, respectively:

$$(2^{d}/q) \cdot x^{i} = \underbrace{\overbrace{\vdots \cdot \cdot \cdot \cdot}^{\lfloor \frac{2^{d} \cdot x^{i}}{q} \rfloor}}_{d} \bullet \underbrace{\overbrace{\vdots \cdot \cdot \cdot \cdot \cdot \cdot}^{\lfloor \frac{2^{d} \cdot x^{i} \mod q}{q} \rfloor_{f}}}_{f} \underbrace{\overbrace{\cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot}^{2^{d+f} \cdot x^{i} \mod q}}_{\infty} . \tag{9}$$

When the quotients are truncated as in Equation 7,  $\lfloor (2^d/q) \cdot x^0 \rfloor_f$  and  $\lfloor (2^d/q) \cdot x^1 \rfloor_f$  produce a strict underestimate of the real quotient  $(2^d/q) \cdot x$ . This underestimate has the effect of truncating the actual quotient  $(2^d/q) \cdot x$ , and possibly omits a carry-in from the additive shares at the *f*-th fractional bit:

$$\lfloor (2^d/q) \cdot x^0 \rfloor_f + \lfloor (2^d/q) \cdot x^1 \rfloor_f = \lfloor (2^d/q) \cdot x \rfloor_f - \frac{\{0,1\}}{2^f} \mod 2^d .$$

(10)

Nevertheless, this underestimate can still be rounded correctly, if f is chosen such that fractional values larger than 0.5 do not underflow below 0.5. Specifically, when  $(2^d/q) \cdot x$

Algorithm 13: MaskedCompress<sub>a</sub> **Input:**  $\mathbf{x}^{\{0:1\}} = (x^0, x^1)$  such that  $x = x^0 + x^1$ ,  $d, f > \log_2(2q)$  **Result:**  $\mathbf{z}^{\{0:1\}} = (z^0, z^1)$  such that  $z = z^0 \oplus z^1 = \text{Compress}_q(x, d)$ 1  $x'^{0} \leftarrow |(2^{d+f} \cdot x^{0})/q| \mod 2^{d+f}$ **2**  $x'^{1} \leftarrow (\lfloor (2^{d+f} \cdot x^{1})/q \rfloor + 2^{f} \cdot 0.5) \mod 2^{d+f}$  $\mathbf{z}^{\{0:1\}} \leftarrow \mathtt{A2B}(\mathbf{x}^{\prime\{0:1\}})$ // (d+f)-bit A2B 4  $\mathbf{z}^{\{0:1\}} \leftarrow \mathbf{z}^{\{0:1\}} \gg f$

takes the edge-case fractional value  $\frac{\left\lceil \frac{q}{2} \right\rceil}{q}$ , it must hold that  $\lfloor \frac{\left\lceil \frac{q}{2} \right\rceil}{q} \rfloor_f - \frac{1}{2^f} \ge 0.5$ . For Kyber, this holds for  $f \ge 13.^4$

We can similarly analyze the rounded quotients of Equation 8. By rounding at the (f+1)-th binary digit, the worst-case rounding error is  $|e_i| < \frac{1}{2f+1}$  for each share-wise quotient.<sup>5</sup> The total rounding error for two shares therefore remains strictly bounded by  $|e| < 2 \cdot \frac{1}{2^{f+1}}$ . To satisfy  $-\frac{1}{2q} \le e < \frac{1}{2q}$ , it suffices that  $f > \log_2(2q)$ , which again results in  $f \ge 13$  for Kyber. As truncation is easier to implement than rounding and results in the same bound, we choose to implement it in our algorithm.

After computing share-wise quotients with a certain precision f, we obtain a 'fixed-point' arithmetic sharing:

$$x^{\prime 0} = \lfloor (2^d/q) \cdot x^0 \rfloor_f \tag{11}$$

$$x^{\prime 1} = \lfloor (2^d/q) \cdot x^1 \rfloor_f \tag{12}$$

$$(2^{d}/q) \cdot x \approx x^{\prime 0} + x^{\prime 1} \bmod 2^{d} , \qquad (13)$$

with d integer bits and f fractional bits. For an appropriately large choice of f, this 'fixed-point' arithmetic sharing allows us to recover the output of  $Compress_{q}(x, d)$ :

$$\operatorname{Compress}_{q}(x,d) = \lceil x'^{0} + x'^{1} \rfloor \mod 2^{d}$$

(14)

$$= |x'^{0} + x'^{1} + 0.5| \mod 2^{d} . \tag{15}$$

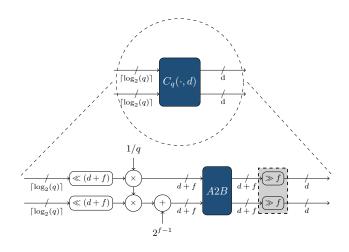

Somewhat surprisingly, we have reduced  $MaskedCompress_{q}$  exactly to the problem of  $MaskedCompress_{2^k}$ . The final output of  $Compress_a(x, d)$  constitutes the upper d bits of the (d+f)-bit arithmetic sharing  $(x'^0, x'^1 + 0.5)$ , which we compute with a (d+f)-bit A2B conversion and subsequent share-wise logical shift. As before, the A2A conversion of [BDK<sup>+</sup>21] is applicable to optimize the computation of the carry-in, but prevents unified hardware in our case.

We illustrate our  $\mathtt{MaskedCompress}_q$  routine in Algorithm 13 and also graphically in Figure 4, using only integer arithmetic and flooring divisions.<sup>6</sup> The simplicity is apparent, requiring only a single A2B call that combines information from the shares. For higherorder security, f must be chosen to tolerate rounding errors from an increasing number of shares. As a result, the required bit-size of the A2B grows logarithmically with the number of shares. For first-order security with f = 13, the largest value for d is  $d_u = 11$  in Kyber-1024, requiring a 24-bit power-of-two A2B conversion. Using our novel  $MaskedCompress_a$ algorithm, masked Kyber does not require any actual  $A2B_q$  conversion.

<sup>&</sup>lt;sup>4</sup>Since  $\frac{1665}{3329} = b0.100000000001...$  as a binary fraction, an underflow is allowed at the 13-th position. <sup>5</sup>More precisely,  $|e_i| \leq \frac{\lfloor \frac{q}{2} \rfloor}{\frac{q}{2^f}}$ .

<sup>&</sup>lt;sup>6</sup>As an implementational note, for d > 7,  $(2^{d+f}) \cdot x^i$  can grow larger than 32-bit. The result must be placed in a  $uint64_t$ , and special care must be exercised that the division of a  $uint64_t$  by the constant qcompiles to a constant-time operation.

Figure 4: MaskedCompress<sub>q</sub>

## 2.3 Masked Equality Test

At the end of the decapsulation, the re-encrypted ciphertext  $\mathbf{c}' = \mathbf{c}'^0 \oplus \mathbf{c}'^1$  must be checked for equality against the input ciphertext  $\mathbf{c}$ . The end result of the check is no longer sensitive, but the re-encrypted ciphertext itself must not be unmasked.

Both first-order and higher-order secure algorithms for masked equality testing have been proposed in [OSPG18] and [BPO<sup>+</sup>20], respectively. In [OSPG18], the main idea is to use an additional hashing step and check whether  $\mathcal{H}(\mathbf{c} \oplus \mathbf{c}'^0)$  equals  $\mathcal{H}(\mathbf{c}'^1)^7$ . The collisionresistance of  $\mathcal{H}$  guarantees that the two hashes are only equal for a valid ciphertext, and the pre-image resistance ensures that the hashes no longer contain exploitable information about  $\mathbf{c}'$ .

Recently, it was shown that both the [OSPG18] and [BPO<sup>+</sup>20] methods leak some information on  $\mathbf{c}'$ , and that this information can be used to significantly decrease the security of the underlying MLWE instance [BDH<sup>+</sup>21]. The method of [OSPG18] contains a flaw because it checks the equality of the two masked ciphertext components  $\mathbf{c}_1'^{\{0:1\}}$  and  $\mathbf{c}_2'^{\{0:1\}}$  separately. The individual equalities are still sensitive, which was already noted by the authors of the masked Saber implementation [BDK<sup>+</sup>21]. Luckily, the method permits a simple fix, by performing the test atomically for both ciphertext components. We take the same approach as [BDK<sup>+</sup>21] and check whether

$$\mathcal{H}(\mathbf{c}_1 \oplus \mathbf{c}_1^{\prime 0} \| \mathbf{c}_2 \oplus \mathbf{c}_2^{\prime 0}) \stackrel{?}{=} \mathcal{H}(\mathbf{c}_1^{\prime 1} \| \mathbf{c}_2^{\prime 1}) \quad .$$

(16)

By performing the hash atomically on the concatenation of both ciphertext components, the leakage present in [OSPG18] can be prevented [BDH<sup>+</sup>21]. By implementing the masked equality test from [OSPG18], we limit this component to first-order side-channel security. While we prefer to use methods that extend to higher orders, the masked equality test of  $[BPO^+20]$  is not applicable to Saber or Kyber due to the ciphertext compression operation. Generalizing this component so that it is extensible to higher masking orders is left as future work.

## 2.4 Comparing Masking for Kyber vs Saber

In Figures 1 and 2, it can be seen that Kyber and Saber have highly similar masked architectures. The difference between MLWE and MLWR is apparent, in the extra XOF,

<sup>&</sup>lt;sup>7</sup>The XOR becomes a subtraction if  $\mathbf{c}'^{\{0:1\}}$  is arithmetically shared as in [OSPG18].

$\Psi_{\eta_2}$ , and B2A<sub>q</sub> calls required to sample the error terms  $\mathbf{e}_1$ , and  $e_2$  for Kyber. B2A<sub>q</sub> has roughly twice the complexity of B2A, essentially because SecAdd<sub>q</sub> makes two calls to SecAdd. Kyber further needs an additional B2A<sub>q</sub> conversion to convert the Boolean masking  $\mathbf{m}^{\{0:1\}}$  back to an arithmetic sharing mod q. This operation is 'free' for Saber, since the required share-wise left-shift  $2^{\epsilon_p-1} \cdot \mathbf{m}^{\{0:1\}}$  already has the added effect of converting to an arithmetic sharing mod p implicitly.

Using our new  $MaskedCompress_q$  algorithm, masked ciphertext compression is remarkably similar for Saber and Kyber. For both, the involved non-linear operation is a power-of-two A2B conversion, where only the high-order bits of the resulting Boolean masking must be kept. However, Saber only requires a 13-bit A2B conversion, whereas Kyber-1024 requires a 24-bit conversion. Moreover, the conversion width for Kyber grows (logarithmically) with the number of shares.

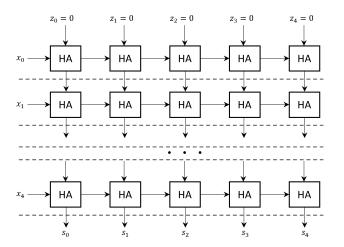

Specialized hardware could be used to favor masking methods for either Saber or Kyber. In this work, our aim is to be generic and support masking for both schemes with identical hardware. Therefore, in Section 4.3, we implement a 32-bit Kogge-Stone SecAdd that supports A2B conversion for both Saber and Kyber. Especially Saber could benefit from a smaller and faster adder, or from A2B/B2A algorithms specialized for power-of-two moduli [BCZ18]. In Section 4.2, we describe a generic hardware architecture for masked binomial sampling. This architecture could in turn be optimized for Kyber, which uses smaller  $\eta$  than Saber.

## 3 HW Accelerators for Linear Operations

In a masked setting, all polynomial arithmetic is duplicated. A hardware accelerator for these operations is therefore increasingly important. As the goal of this work is to mask Kyber and Saber, we build a unified hardware accelerator that efficiently supports polynomial arithmetic for both schemes. A common hardware accelerator for arithmetic operations in Kyber and Saber needs to cover a wide range of different requirements. In this chapter, we present a novel NTT-based hardware accelerator that meets these requirements. Due to the generic design strategy, the developed architecture automatically covers a variety of other lattice-based schemes (see Table 1).

## 3.1 Number Theoretic Transform (NTT)

The NTT is an efficient method to reduce the complexity of the polynomial multiplication from  $\mathcal{O}(n^2)$  to  $\mathcal{O}(n \log_2(n))$ . It is a variant of the Fast Fourier Transform (FFT) with operations in the field  $\mathbb{Z}_q$  instead of the complex numbers.

Let  $a, s \in \mathbb{Z}_q/\phi(x)$  be two ring polynomials of degree n-1. Then the polynomial multiplication using the forward and inverse NTT can be computed with  $c = \text{INVNTT}(\text{NTT}(a) \odot \text{NTT}(s))$ , where  $\odot$  denotes the coefficient-wise multiplication.

In lattice-based cryptography, the product of a polynomial multiplication of length 2n is usually reduced by the cyclotomic polynomial  $\phi(x)$  (frequently  $x^n - 1$  or  $x^n + 1$ ). The polynomial reduction by  $x^n - 1$  is also referred to as positive wrapped convolution and the reduction by  $x^n + 1$  as negative wrapped convolution. Let  $\omega_n \in \mathbb{Z}_q$  be the *n*-th root of unity with  $\omega_n^n = 1 \mod q$  and  $\omega_n^i \neq 1 \mod q$  for  $\forall i \in [0, n-1]$ . The forward transform of the coefficients  $a_i$  and the inverse transform of  $\hat{a}_i$  are computed with

$$\hat{a}_{i} = \sum_{j=0}^{n-1} \gamma^{j} \cdot \omega_{n}^{ij} \cdot a_{j} , \qquad a_{i} = \frac{1}{n} \cdot \gamma^{-i} \sum_{j=0}^{n-1} \omega_{n}^{-ij} \cdot \hat{a}_{j} , \qquad (17)$$

where  $\gamma$  is the 2*n*-th root of unity  $\gamma_n$  for negative wrapped convolutions and  $\gamma = 1$  for positive wrapped convolutions. With pre- and postprocessing using the powers of  $\gamma$  a length-2*n* NTT with zero-padding can be avoided and a length-*n* NTT is sufficient.

| Scheme           | n        | q       | $\phi(x)$   | NTT-based | $\lceil log_2(q') \rceil$ |

|------------------|----------|---------|-------------|-----------|---------------------------|

| NewHope-512/1024 | 512/1024 | 12289   | $x^{n} + 1$ | yes       | 14                        |

| Kyber            | 256      | 3329    | $x^{n} + 1$ | yes       | 12                        |

| Dilithium        | 256      | 8380417 | $x^{n} + 1$ | yes       | 23                        |

| Falcon-512/1024  | 512/1024 | 12289   | $x^{n} + 1$ | yes       | 14                        |

| Saber            | 256      | 8192    | $x^{n} + 1$ | no        | 34                        |

| ntruhps2048509   | 509      | 2048    | $x^{n} - 1$ | no        | 31                        |

| ntruhps2048677   | 677      | 2048    | $x^{n} - 1$ | no        | 32                        |

| ntruhps4096821   | 821      | 4096    | $x^{n} - 1$ | no        | 34                        |

| ntruhrss701      | 701      | 8192    | $x^{n} - 1$ | no        | 36                        |

| LAC-128          | 512      | 251     | $x^{n} + 1$ | no        | 25                        |

| LAC-192/256      | 1024     | 251     | $x^n + 1$   | no        | 26                        |

Table 1: NTT parameters of several lattice-based algorithms.

#### 3.2 Design Rationale - NTT

Table 1 summarizes polynomial arithmetic parameters used in several lattice-based algorithms. While some schemes already use parameters suitable for the NTT, others choose a prime not suitable for a direct application of the NTT.

**NTT with prime lift.** The original prime q can be lifted to any 'NTT friendly' prime  $q' > n \cdot q^2$  for an NTT-based polynomial multiplication. The intermediate values and result of the polynomial multiplication have coefficients not larger than  $n \cdot q^2$ . If q' is set sufficiently large, precision errors caused by the modular arithmetic are avoided [PNPM15]. After polynomial multiplication with the NTT, the coefficients can be reduced by the original prime q. Using signed arithmetic, the maximum absolute value of the coefficients during the computation is  $n \cdot q^2/4$  when the coefficients are represented in [-q/2, q/2). Some schemes always multiply large polynomials with small polynomials sampled from the error distribution, allowing to further decrease the value of q'. However, for schemes as NTRU, large polynomials with coefficients in [0, q) are multiplied with polynomials having the same coefficient range. As in this work all schemes of Table 1 shall be supported by the same hardware architecture and unsigned arithmetic is more suitable for hardware circuits, the rule  $q' > n \cdot q^2$  is applied.

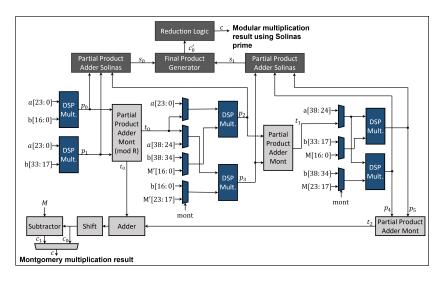

All NTT-based schemes of Table 1 have primes smaller than 23 bits. To cover all ranges, in this work, we develop a flexible Montgomery multiplier for any prime up to 24 bits. For algorithms that are not NTT-based, a lifted prime q' has to be found that covers the remaining algorithms. To allow an easy reduction, the Solinas prime  $q' = 2^{39} - 2^{12} + 1 = 549755809793$  is chosen. For this prime the condition  $q' \equiv 1 \mod 2n$  (the prime has the form  $q' = 2^k p + 1$ ) holds and the *n*-th as well as the 2*n*-th root of unity exists (e.g., for  $n \in [256, 512, 1024, 2048]$ ).

**Positive and negative wrapped convolution.** Choosing  $\gamma = 1$  or  $\gamma = \gamma_n = \sqrt{\omega_n}$  with  $\omega_n^n = 1 \mod q$ ,  $\omega_n^{n-1} = \gamma_n^n = -1 \mod q$ , and  $n = 2^k$  leads to positive and negative wrapped convolutions for NTT-based schemes, respectively. Lifting to a higher prime only works if no reduction errors are introduced during the convolution. Negacyclic convolutions involve negative intermediate results that lead to an erroneous output when reduced by q'. These reductions can be avoided using signed arithmetic. For unsigned arithmetic, polynomial multiplications with polynomials of length n' = 2n, zero-padding, and consecutive polynomial reduction by  $\phi(x)$  can be used. Positive wrapped convolutions can still be realized with an NTT of length n' = n.

**Incomplete NTT.** The prime q is usually chosen such that  $\phi(x)$  can be factored into  $n = 2^k$  linear terms  $\phi(x) = \prod_{i=0}^{n-1} \phi_i(x) \mod q$ . This allows the full application of the NTT and the basecase multiplication of two transformed polynomials corresponds to a simple coefficient-wise multiplication. The concept of the incomplete NTT for lattice-based

cryptography was first proposed in [LS19] and a similar concept was later adopted to the second round Kyber specification. Kyber reduced its prime value (consequently key and ciphertext sizes) and chose a value where the *n*-th root of unity exists but not the 2*n*-th root of unity. This prevents applying a full NTT and only l-1 layers of the NTT are applied resulting into n/2 polynomials of degree two. More precisely, the cyclic polynomial is factored to  $\phi(x) = x^n + 1 = \prod_{i=0}^{n/2-1} (x^2 - \omega_n^{2i+1}) = \prod_{i=0}^{n/2-1} (x^2 - \omega_n^{2br(i)+1})$  with *br* denoting

the bit reversal function.

**NTT algorithms.** When exploiting symmetry, periodicity, and scale properties of the Fourier transformation, the complexity of Equation 17 can be reduced with an divideand-conquer approach from  $\mathcal{O}(n^2)$  to  $\mathcal{O}(n \log_2(n))$ . The two most common methods for splitting a large Fourier transform into smaller pieces are the Cooley-Tukey (CT) [CT65] and the Gentleman-Sande (GS) [GS66] algorithms. The butterfly operation, which is the main operation of these algorithms, consists of simple arithmetic in  $\mathbb{Z}_q$ . The Cooley-Tukey decimation-in-time (DIT) approach computes  $x' \leftarrow x + y \cdot \omega$  and  $y' \leftarrow x - y \cdot \omega$  with  $\omega, x, y \in \mathbb{Z}_q$  and  $\omega$  usually a power of  $\omega_n$  (also known as Twiddle factor). The Gentleman-Sande decimation-in-frequency (DIF) approach computes  $x' \leftarrow x + y$  and  $y' \leftarrow (x - y) \cdot \omega$ .

Different in-place variants of the Cooley-Tukey and Gentleman-Sande algorithms exist, denoted as  $\text{NTT}_{br\to no}^{CT}$ ,  $\text{NTT}_{no\to br}^{GS}$ ,  $\text{NTT}_{no\to br}^{GS}$ , and  $\text{NTT}_{no\to br}^{GS}$ , where, e.g.,  $no \to br$  indicates that the input is in normal and the output in bit-reversed order. The bit-reversal can be completely avoided with a combination of the different variants  $\text{NTT}_{no\to br}^{CT}$  and  $\text{INVNTT}_{br\to no}^{GS}$  [POG15].

Likewise to previous works, we use different algorithms for the forward and inverse NTT to avoid the bit-reversal step, although the bit-reversal operation is simple in hardware. Using a DIT algorithm for the forward transform and a DIF algorithm for the inverse transform has the further advantage that the multiplications by the powers of  $\gamma_n$  can be integrated into precomputed tables for the Twiddle factors.

Algorithms 14 and 15 illustrate the operations for our flexible NTT. Starting with the original NTT/INVNTT algorithms, we modify the algorithms to support an early abort for an incomplete NTT, as required by Kyber. The incomplete NTT can be activated using the early\_abort signal. Moreover, we integrated support for either positive or negative wrapped convolutions. The wrapping method can be switched using the negacyclic signal. Thus, all schemes of Table 1 can use the same algorithms. Note that the INVNTT requires a final scaling by  $n^{-1}$ . For NTT-based schemes, the Twiddle table is stored in Montgomery domain in order to make use of a flexible Montgomery multiplier. In negacyclic NTT-based schemes, the Twiddle table contains n (n/2 at early aborts) merged values for the powers of  $\omega_n$  and  $\gamma_n$  in bit-reversed order and the same amount of precomputed values for the inverse transform. For schemes with positive wraparound or schemes not based on NTT, n precomputed values of the powers of  $\omega_n$  are stored in the Twiddle table.

## 3.3 Architecture - NTT

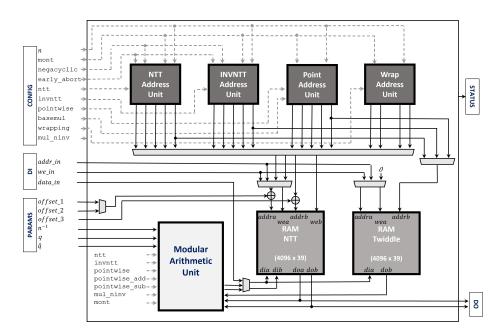

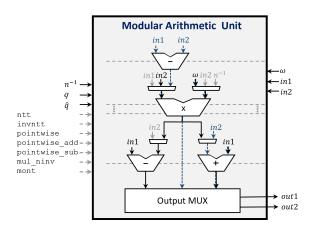

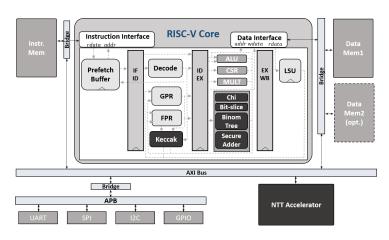

Designing an efficient and flexible NTT with support of all mentioned lattice-based schemes requires new design approaches and multiple components. Figure 5 illustrates the hardware architecture of our proposed loosely coupled NTT accelerator. It consists of seven different main modules: two RAM blocks (NTT and Twiddle RAM), four address units (NTT, INVNTT, Point, and Wrap), and a Modular Arithmetic Unit.

**NTT and Twiddle RAM.** The two memory blocks are used for storing the input/output coefficients and the precomputed Twiddle table, respectively. The size of these memory blocks is chosen large enough to support all parameter sets. To increase the

| Algorithm 14: NTT transform                                 |

|-------------------------------------------------------------|

| <b>Input:</b> $a \in \mathbb{Z}_q/\phi(x)$ , twiddle_table, |

| early_abort, negacyclic                                     |

| <b>Result:</b> $\hat{a} \in \mathbb{Z}_q/\phi(x)$           |

| 1 if early_abort then                                       |

| 2 $stop \leftarrow n/2$                                     |

| 3 else                                                      |

| $4     stop \leftarrow n$                                   |

| 5 end                                                       |

| 6 $t \leftarrow n$                                          |

| 7 for $m = 1$ to $stop - 1$ by $m = 2m$ do                  |

| $\mathbf{s} \mid t \leftarrow t/2$                          |

| 9 for $i = 0$ to $m - 1$ by 1 do                            |

| 10 $j_1 \leftarrow 2it, j_2 \leftarrow j_1 + t$             |

| 11 if negacyclic then                                       |

| 12 $m' \leftarrow m$                                        |

| 13 else                                                     |

| 14 $m' = 0$                                                 |

| 15 end                                                      |

| $16 \qquad \qquad \omega \leftarrow twiddle\_table[m'+i]$   |

| 17 for $j = j_1$ to $j_2 - 1$ by 1 do                       |

| $18 \qquad z_1 \leftarrow a_{j+t} \cdot \omega \mod q$      |

| $19 \qquad \qquad a_j \leftarrow a_j + z_1 \mod q$          |

| $20 \qquad \qquad a_{j+t} \leftarrow a_j - z_1 \mod q$      |

| 21 end                                                      |

| 22 end                                                      |

| 23 end                                                      |

|                                                             |

```

Algorithm 15: INVNTT transform

Input: \hat{a} \in \mathbb{Z}_q/\phi(x), invtwiddle_table,

\verb"early_abort", \verb"negacyclic"

Result: a \in \mathbb{Z}_q/\phi(x)

1 if early_abort then

2

m \leftarrow n/2, t \leftarrow 2, k \leftarrow 0

з else

\mathbf{4} \quad | \quad m \leftarrow n, \ t \leftarrow 1

5 end

6 for m to m > 1 by m = m/2 do

7

j_1 \leftarrow 0

8

9

m' \leftarrow m/2

else

10

11

| m' = 0

end

\mathbf{12}

13

for i = 0 to m/2 - 1 by 1 do

j_2 \leftarrow j_1 + t

14

if early\_abort then

\mathbf{15}

\omega \leftarrow invtwiddle\_table[k_{++}]

16

17

else

18

\omega \leftarrow invtwiddle\_table[m'+i]

end

19

20

for j = j_1 to j_2 - 1 by 1 do

z_1 \leftarrow a_j, \ z_2 \leftarrow a_{j+t}

21

22

a_j \leftarrow z_1 + z_2 \mod q

a_{j+t} \leftarrow (z_1 - z_2) \cdot \omega \mod q

23

\mathbf{24}

\mathbf{end}

j_1 \leftarrow j_1 + 2t

\mathbf{25}

\mathbf{26}

\mathbf{end}

t \leftarrow 2t

27

28 end

```

Figure 5: Loosely coupled NTT Unit (dashed lines for configuration signals).

Algorithm 16: Basecase multiplication (incomplete NTT) **Input:**  $\hat{f}, \hat{g} \in \mathbb{Z}_q/\phi(x)$ , twiddle\_table, invtwiddle\_table **Result:**  $\hat{h} = \hat{f} \circ \hat{g} \in \mathbb{Z}_q/\phi(x)$ 1 for i = 0 to n/4 by 4 do  $\omega \leftarrow twiddle\_table[n/4+i]$ 2  $\hat{h}_{4i} \leftarrow \hat{f}_{4i+1} \cdot \hat{g}_{4i+1} \cdot \omega + \hat{f}_{4i} \cdot \hat{g}_{4i} \mod q$ 3  $\hat{h}_{4i+1} \leftarrow \hat{f}_{4i} \cdot \hat{g}_{4i+1} + \hat{f}_{4i+1} \cdot \hat{g}_{4i} \mod q$ 4  $\omega \leftarrow invtwiddle\_table[n/4-i-1]$ 5  $\hat{h}_{4i+2} \leftarrow \hat{f}_{4i+3} \cdot \hat{g}_{4i+3} \cdot \omega + \hat{f}_{4i+2} \cdot \hat{g}_{4i+2} \mod q$ 6  $\hat{h}_{4i+3} \leftarrow \hat{f}_{4i+2} \cdot \hat{g}_{4i+3} + \hat{f}_{4i+3} \cdot \hat{g}_{4i+2} \mod q$ 7 s end

efficiency, the dual-port capabilities of the RAM blocks are exploited. The PKE/KEM schemes usually have coefficients of less than 16 bits. As the deployed system is based on a 32-bit architecture, the input *data\_in* (and the output) can contain two coefficients in one word.

NTT/INVNTT Address Unit. It generates the two read and write addresses to load and store two coefficients as well as the read address for the Twiddle factor according to Algorithms 14 and 15. The signals ntt and invntt trigger the corresponding address computations. Optionally, early\_abort and negacyclic can be set. The signal mont is used to select the number of pipeline stages to delay the write signals according to the delay in the arithmetic units.

**Point Address Unit.** It computes the addresses for pointwise multiplications, additions, and subtractions. The signal **basemul** is used to select basecase multiplications at schemes with early abort. Let  $f, g \in \mathbb{Z}_q/\phi(x)$  and let  $\operatorname{NTT}(f) \circ \operatorname{NTT}(g) = \hat{f} \circ \hat{g} = \hat{h}$  denote the basecase multiplication with n/2 products. These products are computed with