# Perfectly Secure Oblivious Parallel RAM

T-H. Hubert Chan<sup>1</sup>, Kartik Nayak<sup>2,3</sup>, and Elaine Shi<sup>4</sup>

<sup>1</sup> The University of Hong Kong, hubert@cs.hku.hk <sup>2</sup> University of Maryland,

<sup>3</sup> VMware Research, nkartik@vmware.com

<sup>4</sup> Cornell University, elaine@cs.cornell.edu

Abstract. We show that PRAMs can be obliviously simulated with perfect security, incurring only  $O(\log N \log \log N)$  blowup in parallel runtime,  $O(\log^3 N)$  blowup in total work, and O(1) blowup in space relative to the original PRAM. Our results advance the theoretical understanding of Oblivious (Parallel) RAM in several respects. First, prior to our work, no perfectly secure Oblivious Parallel RAM (OPRAM) construction was known; and we are the first in this respect. Second, even for the sequential special case of our algorithm (i.e., perfectly secure ORAM), we not only achieve logarithmic improvement in terms of space consumption relative to the state-of-the-art, but also significantly simplify perfectly secure ORAM constructions. Third, our perfectly secure OPRAM scheme matches the parallel runtime of earlier statistically secure schemes with negligible failure probability. Since we remove the dependence (in performance) on the security parameter, our perfectly secure OPRAM scheme in fact asymptotically outperforms known statistically secure ones if (sub-)exponentially small failure probability is desired. Our techniques for achieving small parallel runtime are novel and we employ special expander graphs to derandomize earlier statistically secure OPRAM techniques — this is the first time such techniques are used in the constructions of ORAMs/OPRAMs.

## 1 Introduction

Oblivious RAM (ORAM), originally proposed in the ground-breaking work by Goldreich and Ostrovsky [21, 22], is an algorithmic technique that transforms any RAM program to a secure version, such that an adversary learns nothing about the secret inputs from observing the program's access patterns to memory. The parallel extension of ORAM was first phrased by Boyle, Chung, and Pass [6]. Similar to ORAM, an Oblivious Parallel RAM (OPRAM) compiler transforms a Parallel RAM (PRAM) program into a secure form such that the resulting PRAM's access patterns leak no information about secret inputs. ORAMs and OPRAMs have been recognized as powerful building blocks in both theoretical applications such as multi-party computation [5, 25, 32], as well as in  $\mathbf{2}$

practical applications such as cloud outsourcing [13,40,43], and secure processor design [16,17,31,33,38].

Henceforth in this paper, we consider ORAMs to be a special case of OPRAMs, i.e., when both the original PRAM and the OPRAM have only one CPU. To characterize an OPRAM scheme's overhead, we will use the standard terminology total work blowup to mean the multiplicative increase in total computation comparing the OPRAM and the original PRAM; and we use the term depth blowup to mean the multiplicative increase in parallel runtime comparing the OPRAM and the original PRAM — assuming that the OPRAM may employ more CPUs than the original PRAM to help parallelize its computation [7]. Note that for the case of sequential ORAMs, total work blowup is equivalent to the standard notion of simulation overhead [21, 22], i.e., the multiplicative increase in runtime comparing the ORAM and the original RAM. Finally, we use the term space blowup to mean the multiplicative blowup in space when comparing the OPRAM (or ORAM) and that of the original PRAM (or RAM).

The original ORAM schemes, proposed by Goldreich and Ostrovsky [21,22], achieved poly-logarithmic overheads but required the usage of pseudo-random functions (PRFs); thus they defend only against computationally bounded adversaries. Various subsequent works [2, 9, 11, 12, 39, 41, 42], starting from Ajtai [2] and Damgård et al. [12] investigated information-theoretically secure ORAM/OPRAM schemes, i.e., schemes that do not rely on computational assumptions and defend against even unbounded adversaries. As earlier works point out [2, 12], the existence of efficient ORAM schemes without computational assumptions is not only theoretically intriguing, but also has various applications in cryptography. For example, information-theoretically secure ORAM schemes can be applied to the construction of efficient RAM-model, informationtheoretically secure multi-party computation (MPC) protocols [4]. Among known information-theoretically secure ORAM/OPRAM schemes [2,6,9–12,39,41,42], almost all of them achieve only *statistical* security [2,6,9–11,39,41,42], i.e., there is still some non-zero failure probability — either correctness or security failure — but the failure probability can be made negligibly small in N where N is the RAM/PRAM's memory size. Damgård et al. [12] came up with the first *perfectly* secure ORAM construction — they achieve zero failure probability against computationally unbounded adversaries. Although recent works have constructed statistically secure OPRAMs [6,9,10], there is no known (non-trivial) perfectly secure OPRAM scheme to date.

*Motivation for perfect security.* Perfectly secure ORAMs/OPRAMs are theoretically intriguing for various reasons:

1. First, to achieve  $2^{-\kappa}$  failure probability (either in security or in correctness), the best known statistically secure OPRAM scheme [7, 9] incurs a  $O(\kappa \log N)$  total work blowup and  $O(\log \kappa \log N)$  depth blowup where N is the PRAM's memory size. Although for negligibly small in N failure probability the blowups are only poly-logarithmic in N, they can be as large as  $N^c$  for some constant c < 1 if one desires (sub-)exponentially small failure probability in N.

- 2. Second, perfectly secure ORAM schemes have been used as a building block in recent results on oblivious algorithms [3, 39] and searchable encryption schemes [14]. Typically these algorithmic constructions rely on divide-andconquer to break down a problem into smaller sizes and then apply ORAM to a small instance — since the instance size N is small (e.g., logarithmic in the security parameter), negligible in N failure probability is not sufficient and thus these works demand *perfectly secure* ORAMs/OPRAMs and existing statistically secure schemes result in asymptotically poorer performance.

- 3. Third, understanding the boundary of perfect and statistical security has been an important theoretical question in cryptography. For example, a longstanding open problem in cryptography is to separate the classes of languages that admit perfect ZK and statistical ZK proofs. For ORAMs/OPRAMs too, it remains open whether there are any separations between statistical and perfect security (and we believe that this is an exciting future direction). Perfect security is also useful in other contexts such as multi-party computation (MPC). For example, Ishai et al. [28] and Genkin et al. [19] show that perfectly secure MPC is required to achieve their respective goals matching the "circuit complexity" of the underlying application. Perfectly secure ORAMs/OPRAMs can enable perfectly secure RAM-model MPC, and thus we believe that they can be an important building block in other areas of theoretical cryptography.

### 1.1 Our Results and Contributions

In this paper, we prove the following result which significantly advances our theoretical understanding of *perfectly* secure ORAMs and OPRAMs in multiple respects. We present the informal theorem statement below and then discuss its theoretical significance.

**Theorem 1 (Informal statement of main theorem).** Any PRAM that consumes N memory blocks each of which is at least  $\log N$ -bits  $\log 5$  can be simulated by a perfectly oblivious PRAM, incurring  $O(\log^3 N)$  total work blowup,  $O(\log N \log \log N)$  depth blowup, and O(1) space blowup.

The above theorem improves the theoretical state of the art on perfectly secure ORAMs/OPRAMs in multiple dimensions:

- 1. First, our work gives rise to the first perfectly secure (non-trivial) OPRAM construction. No such construction was known before and it is not clear how to directly parallelize the perfectly secure ORAM scheme by Damgård et al. [12].

- 2. Second, even for the sequential special case, we improve Damgård et al. [12] asymptotically by reducing a  $\log N$  factor in the ORAM's space consumption.

- 3. Third, our perfectly secure OPRAM's parallel runtime matches the best known statistically secure construction [7,9] for negligibly small in N failure probabilities;

<sup>&</sup>lt;sup>5</sup> All existing ORAM and OPRAM works [21–23, 30, 39] make this assumption.

- 4 T-H. Hubert Chan, Kartik Nayak, and Elaine Shi

- 4. Finally, when (sub-)exponentially small (in N) failure probabilities are required, our perfectly secure OPRAM scheme asymptotically outperforms all known statistically secure constructions both in terms of total work blowup and depth blowup. For example, suppose that we require  $2^{-\kappa}$  failure probability and  $N = \text{poly}(\kappa)$  — then all known statistically secure OPRAM constructions [6,9,10] would incur at least  $N^c$  total work blowup and  $\Omega(\log^2 N)$ depth blowup and thus our new perfectly secure OPRAM construction is asymptotically better for this scenario.

Theorem 1 applies to general block sizes. We additionally show that for sufficiently large block sizes, there exists a perfectly secure OPRAM construction with  $O(\log^2 N)$  total work blowup and  $O(\log m + \log \log N)$  depth blowup where m denotes the number of CPUs of the original PRAM (Corollary 2). Finally, we point out that this work focuses mostly on the theoretical understanding of perfect security in ORAMs/OPRAMs, and we leave it as a future research direction to investigate their practical performance (see also Section 8).

Technical highlights. Our most novel and non-trivial technical contribution is the use of expander graphs techniques, allowing our OPRAM to achieve as small as  $O(\log N \log \log N)$  depth blowup. To the best of our knowledge, this is the first time such techniques have been used in the construction of ORAM/OPRAM schemes. Besides this novel technique, our scheme requires carefully weaving together many algorithmic tricks that have been used in earlier works [7,9,21,22]

### 1.2 Related Work

Oblivious RAM (ORAM) was first proposed in a ground-breaking work by Goldreich and Ostrovsky [21, 22]. Goldreich and Ostrovsky first showed a computationally secure ORAM scheme with poly-logarithmic simulation overhead. Therefore, one interesting question is whether ORAMs can be constructed without relying on computational assumptions. Ajtai [2] answered this question and showed that statistically secure ORAMs with poly-logarithmic simulation overhead exist. Although Ajtai removed computational assumptions from ORAMs, his construction has a (negligibly small) statistical failure probability, i.e., with some negligibly small probability, the ORAM construction can leak information. Subsequently, Shi et al. [39] proposed the tree-based paradigm for constructing statistically secure ORAMs. Tree-based constructions were later improved further in several works [9,11,20,41,42], and this line of works improve the practical performance of ORAM by several orders of magnitude in comparison with earlier constructions. It was also later understood that the tree-based paradigm can be used to construct computationally secure ORAMs saving yet another log log factor in cost in comparison with statistical security [9,15].

Perfect security requires that the (oblivious) program's memory access patterns be *identically distributed* regardless of the inputs to the program; and thus with probability 1, no information can be leaked about the secret inputs to the program. Perfectly secure ORAM was first studied by Damgård et al. [12]. Their construction achieves  $O(\log^3 N)$  simulation overhead and  $O(\log N)$  space blowup relative to the original RAM program. Their construction is a Las Vegas algorithm and there is a negligibly small failure probability that the algorithm exceeds the stated runtime. Raskin et al. [37] and Demertzis et al. [14] achieve a *worst-case* bandwidth of  $O(\sqrt{N} \frac{\log N}{\log \log N})$  and  $O(N^{1/3})$ , respectively. As mentioned, even for the sequential case, our paper asymptotically improves Damgård et al.'s result [12] by avoiding the  $O(\log N)$  blowup in space; and moreover, our ORAM construction is conceptually simpler than that of Damgård et al.'s.

Oblivious Parallel ORAM (OPRAM) was first proposed in an elegant work by Boyle, Chung, and Pass [6], and subsequently improved in several followup works [7–10, 35]. All known results on OPRAM focus on the statistically secure or the computationally secure setting. To the best of our knowledge, until this paper, we know of no efficient OPRAM scheme that is perfectly secure. Chen, Lin and Tessaro [10] introduced a generic method to transform any ORAM into an OPRAM at the cost of a log N blowup. Their techniques achieve *statistical* security since security (or correctness) is only guaranteed with high probability (specifically, when some queue does not become overloaded in their scheme).

Defining a good performance metric for OPRAMs turned out to be more interesting and non-trivial than for ORAMs. Boyle et al. [6] were the first to define a notion of simulation overhead for OPRAM: if an OPRAM's simulation overhead is X, it means that if the original PRAM consumes m CPUs and completes in parallel runtime T, then the oblivious counterpart must complete within  $X \cdot T$  time also consuming m CPUs. The recent work of Chan, Chung, and Shi [7] observes that if the OPRAM could consume more CPUs than the original PRAM, then the oblivious simulation can benefit from the additional parallelism and be additionally sped up by asymptotic factors. Under the assumption that the OPRAM can consume more CPUs than the original PRAM, Chan, Chung, and Shi [7,9] show that statistically secure OPRAM schemes can be constructed with  $O(\log^2 N)$  blowup in total work and only  $\tilde{O}(\log N)$  blowup in depth (where depth characterizes the parallel runtime of a program assuming ample number of CPUs). Our paper is the first to construct an OPRAM scheme with perfect security, and our OPRAM's depth matches existing schemes with statistical security assuming negligible in N security failure; however, if (sub-)exponentially small failure probability is required, our new OPRAM scheme can asymptotically outperform all known statistically secure OPRAMs!

## 2 Technical Roadmap

In this section, we present an informal roadmap of our technical approach to aid understanding.

### 2.1 Simplified Perfectly Secure ORAM with Asymptotically Smaller Space

First, we propose a new perfectly secure ORAM scheme that is conceptually simpler than that of Damgård et al. [12] and asymptotically gains a logarithmic

factor in space. Our construction is inspired by the hierarchical ORAM paradigm originally proposed by Goldreich and Ostrovsky [21,22]. However, most existing hierarchical ORAMs achieve only computational security since they rely on a pseudorandom function (PRF) for looking up hash tables in the hierarchical data structure. Thus our focus is how to get rid of this PRF and achieve perfect security.

Background: hierarchical ORAM. The recent work by Chan et al. [8] gave a clean and modular exposition of the hierarchical paradigm. A hierarchical ORAM consists of  $O(\log N)$  levels that are geometrically increasing in size. Specifically, level i is capable of storing  $2^i$  memory blocks. One could think of this hierarchical data structure as a hierarchy of stashes where smaller levels act as stashes for larger levels. In existing schemes with computational security, each level is an oblivious hash-table [8]. To access a block at logical address addr, the CPU sequentially looks up every level of the hierarchy (from small to large) for the logical address addr. The physical location of a logical address addr within the oblivious hash-table is determined using a PRF whose secret key is known only to the CPU but not to the adversary. Once the block has already been found in some level, for all subsequent levels the CPU would just look for a dummy element, denoted by  $\perp$ . When a requested block has been found, it is marked as deleted in the corresponding level where it is found. Every  $2^i$  memory requests, we perform a rebuild operation and merge all levels smaller than i (including the block just fetched and possibly updated if this is a write request) into level i — at this moment, the oblivious hash-table in level i is rebuilt, where every block's location in the hash table is determined using a PRF.

As Chan et al. [8] point out, the hierarchical ORAM paradigm effectively reduces the problem of constructing ORAM to constructing an oblivious hash-table supporting two operations: 1) **rebuild** takes in a set of blocks each tagged with its logical address, and constructs a hash-table data structure that facilitates lookups later; and 2) **lookup** takes a request that is either a logical address **addr** or dummy (denoted  $\perp$ ), and returns the corresponding block requested. Obliviousness (defined w.r.t. the joint access patterns of the rebuild and lookup phases) is guaranteed as long as during the life-time of the oblivious hash-table, the sequence of lookup requests never ask for the same real element twice — and this invariant is guaranteed by the specific way the hierarchical ORAM framework uses the oblivious hash-table as a building block (more specifically, the fact that once a block is found, it is moved to a smaller level and a dummy block is requested from all subsequent levels).

Removing the PRF. As mentioned, an oblivious hash-table relies on a PRF to determine each block's location within a hash-table instance; and both the rebuilding phase and the lookup phase use the same PRF for placing and fetching blocks respectively. Since we wish to achieve perfect security, we would like to remove the PRF. One simple idea is to randomly permute all blocks within a level — this way, each lookup of a real block would visit a random location and we could hope to retain security as long as every real block is requested at

most once for every level (in between rebuilds)<sup>6</sup>. Using techniques from earlier works [7, 9], it is possible to obliviously perform such a random permutation without disclosing the permutation; however, difficulty arises when one wishes to perform a look up — if blocks are randomly permuted within a level during rebuild, lookup must know where each block resides to proceed successfully. Thus if the CPU could hold a position map for free to remember where each block is in the hierarchical data structure, the problem would have been resolved: during every lookup, the CPU could first look up the physical location of the logical address requested, and then proceed accordingly.

Actually storing such a position map, however, would consume too much CPU space. To avoid storing this position map, we are inspired by the recursion technique that is commonly adopted by tree-based ORAM schemes [39] — however, as we point out soon, making the recursion idea work for the hierarchical ORAM paradigm is more sophisticated. The high-level idea is to recursively store the position map in a smaller ORAM rather than storing it on the CPU side; we could then recurse and store the position map of the position map in an even smaller ORAM, and so on — until the ORAM's size becomes O(1) at which point we would have the CPU store the entire ORAM. Henceforth, we use the notation ORAM<sub>D</sub> to denote the ORAM that stores the actual data blocks where  $D = O(\log N)$ ; and we use ORAM<sub>d</sub> to denote the ORAM at depth d of this recursion where  $d \in [0..D - 1]$ . Thus, the larger d is, the larger the ORAM.

Although this recursion idea was very simple in the tree-based paradigm, it is not immediately clear how to make the same recursion idea work in the hierarchical ORAM paradigm. One trickiness arises since in a hierarchical ORAM, every  $2^i$  requests, the ORAM would reshuffle and merge all levels smaller than *i* into level *i* — this is called a rebuild of level *i*. When a level-*i* rebuild happens, the position labels in the position-map ORAM must be updated as well to reflect the blocks' new locations. In a similar fashion, the position labels in all of ORAM<sub>0</sub>, ORAM<sub>1</sub>, ..., ORAM<sub>D-1</sub> must be updated. We make the following crucial observation that will enable a *coordinated rebuild* technique which we will shortly explain:

(Invariant necessary for coordinated rebuild:) If a data block resides at level i of  $ORAM_D$ , then its position labels in all recursion depths must reside in level i or smaller<sup>7</sup>.

This invariant enables a *coordinated rebuild* technique: when the data ORAM (i.e.,  $ORAM_D$ ) merges all levels smaller than *i* into level *i*, all smaller recursion depths would do the same (unless the recursion depth is too small and does not have level *i*, in which case the entire ORAM would be rebuilt). During this coordinated rebuild,  $ORAM_D$  would first perform its rebuild, and propagate the position labels of all blocks involved in the rebuild to recursion depth D - 1;

<sup>&</sup>lt;sup>6</sup> As we point out later, randomly permuting real blocks is in fact not sufficient; we also need to allow dummy lookups by introducing an oblivious dummy linked list.

<sup>&</sup>lt;sup>7</sup> A similar observation was adopted by Goodrich et al. [24] in their statistically secure ORAM construction.

8

then  $\mathsf{ORAM}_{D-1}$  would perform its rebuild based on the position labels learned from  $\mathsf{ORAM}_D$ , and propagate the new position labels involved to recursion depth D-2, and so on. As we shall discuss in the technical sections, rebuilding a level (in any recursion depth) can be accomplished through the help of O(1) oblivious sorts and an oblivious random permutation.

Handling dummy blocks with oblivious linked lists. The above idea almost works, but not quite so. There is an additional technical subtlety regarding how to handle and use dummy blocks. Recall that during a memory access, if a block requested actually resides in a hierarchical level, we would read the memory location that contains the block (and this memory location could be retrieved through a special recursive position map technique). If a block does not reside in a level (or has been found in a smaller level), we still need to read a dummy location within the level to hide the fact that the block does not reside within the current level.

Recall that the *i*-th level must support up to  $2^i$  lookups before the level is rebuilt. Thus, one idea is to introduce  $2^i$  dummy blocks, and obliviously and randomly permute all blocks, real and dummy alike, during the rebuild. All dummy blocks may be indexed by a dummy counter, and every time one needs to look up a dummy block in a level, we will visit a new dummy block. In this way, we can retain obliviousness by making sure that every real block and every dummy block is visited at most once before the level is rebuilt again.

To make this idea fully work, there must be a mechanism for finding out where the next dummy block is every time a dummy lookup must be performed. One naïve idea would be to use the same recursion technique to store position maps for dummy blocks too — however, since each memory request might involve reading  $O(\log N)$  dummy blocks, one per level, doing so would incur extra blowup in runtime and space. Instead, we use an *oblivious dummy linked list* to resolve this problem — this oblivious dummy linked list is inspired by technical ideas in the Damgård et al. construction [12]. In essence, each dummy block stores the pointer to the next dummy block, and the head pointer of the linked list is stored at a designated memory location and updated upon each read of the linked list. In the subsequent technical sections, we will describe how to rely on oblivious sorting to rebuild such an oblivious dummy linked list to support dummy lookups.

Putting it altogether. Putting all the above ideas together, the formal presentation of our perfectly secure ORAM scheme adopts a modular approach<sup>8</sup>. First, we define and construct an abstraction called an "oblivious one-time memory". An oblivious one-time memory allows one to obliviously create a data structure given a list of input blocks. Once created, one can look up real or dummy blocks in the data structure, and to look up a real block one must provide a correct position label indicating where the block resides (imagine for now that the position

<sup>&</sup>lt;sup>8</sup> In fact, later in our paper, we omit the sequential version and directly present the parallel version of all algorithms.

label comes from an "oracle" but in the full ORAM scheme the position label comes from the recursion). An oblivious one-time memory retains obliviousness as long as every real block is looked up at most once and moreover, dummy blocks are looked up at most n times where n is a predetermined parameter (that the scheme is parametrized with).

Once we have this "oblivious one-time memory" abstraction, we show how to use it to construct an intermediate abstraction referred to as a "position-based ORAM". A position-based ORAM contains a hierarchy of oblivious one-time memory instances, of geometrically growing sizes. A position-based ORAM is almost a fully functional ORAM except that we assume that upon every memory request, an "oracle" will somehow provide a correct position label indicating where the requested block resides in the hierarchy.

Finally, we go from such a "position-based ORAM" to a fully functional ORAM using the special recursive position-map technique as explained. At this point, we have constructed a perfectly secure ORAM scheme with  $O(\log^3 N)$  simulation overhead. Specifically, one log N factor arises from the log N depths of recursion, the remaining  $\log^2 N$  factor arises from the cost of the ORAM at each recursion depth. Intuitively, our perfectly secure ORAM is a logarithmic factor more expensive than existing computationally-secure counterparts in the hierarchical framework [8, 23, 30] since the computationally-secure schemes [8, 23, 30] avoid the recursion by adopting a PRF to compute the pseudorandom position labels of blocks.

### 2.2 Making Our ORAM Scheme Parallel

Our next goal is to make our ORAM scheme parallel. Instead of compiling a sequential RAM program to a sequential ORAM, we are now interested in compiling a PRAM program to an OPRAM.

When the OPRAM Consumes the Same Number of CPUs as the PRAM. Suppose that the original program is a PRAM that completes in T parallel steps consuming m CPUs. We now would like to parallelize our earlier ORAM scheme and construct an OPRAM that completes in  $T \cdot O(\log^3 N)$  parallel steps consuming also exactly m CPUs. To accomplish this, first, we need to parallelize within each position-based ORAM so m CPUs can perform work concurrently. This is not too difficult to accomplish given the simplicity of our position-based ORAM construction. Next, when m CPUs have all fetched position labels at one recursion depth, they need to pass these position labels to the CPUs at the next depth. The main technique needed here is oblivious routing: when the m CPUs at recursion depth d have fetched the position labels for the next recursion depth, the m CPUs at depth. As shown in earlier works [6,7,9], such oblivious routing can be accomplished with m CPUs in  $O(\log m)$  parallel steps.

We stress that the simplicity of our sequential ORAM construction makes it easy to parallelize — in comparison, we are not aware how to parallelize Damgård et al. [12]'s construction<sup>9</sup>.

When the OPRAM May Consume Unbounded Number of CPUs. The more interesting question is the following: *if the OPRAM is allowed to consume more CPUs than the original PRAM, can we further reduce its parallel runtime?* If so, it intuitively means that the overheads arising due to obliviousness are parallelizable in nature. This model was first considered by Chan et al. [7] and can be considered as a generalization of the case when the OPRAM must consume the same number of CPUs as the original PRAM.

So far, in our OPRAM scheme, although within each recursion depth, up to m requests can be served concurrently, the operations over all  $O(\log N)$  recursion depths must be performed sequentially. There are two reasons that necessitate this sequentiality:

- 1. Fetch phase: first, to fetch from recursion depth d, one must wait for the appropriate position labels to be fetched from recursion depth d 1 and routed to recursion depth d;

- 2. Maintain phase: recall that coordinated rebuilding (see Section 2.1) is performed across all recursion depths in the reverse direction: recursion depth dmust rebuild first and then propagate the new positions labels back to recursion depth d-1 before d-1 can rebuild (recall that recursion depth d-1must store the position labels for blocks in depth d).

Note that for the fetch phase, oblivious routing between any two adjacent recursion depths would consume  $O(\log m)$  depth; for the maintain phase, rebuilding a hierarchical level can consume up to  $O(\log N)$  depth (due to oblivious sorting of up to O(N) blocks). Thus, the current OPRAM algorithm incurs a depth blowup of  $O(\log^2 N)$  for moderate sizes of m, e.g., when  $\log m = \Theta(\log N)$ . Our next goal is to reduce the depth blowup to  $\widetilde{O}(\log N)$ , and this turns out to be highly non-trivial.

Reducing the depth of the fetch phase with expander graphs. Using the recursion technique, it seems inherent that one must fetch from smaller recursion depths before embarking on larger ones. To reduce the depth of the fetch phase, we ask whether the depth incurred by oblivious routing in between adjacent recursion depths can be reduced. In the statistically and computationally secure settings, the recent work by Chan, Chung, and Shi have tried to tackle a similar problem

<sup>&</sup>lt;sup>9</sup> In Damgård et al. [12], the shuffle phase incurs an  $O(\log^3 N)$  depth which is the same as the overhead for accessing a block. Specifically, a log N factor arises due to oblivious sorting, a log N factor due to the existence of hierarchies, and another log N factor due to the extra log N dummies stored for every real element. Though an offline/online technique like ours may be conceivable for their scheme, the existence of the extra log N dummies makes it inherently hard to improve the depth by another log N factor.

for tree-based OPRAMs [7]. Their idea is to construct an offline/online routing algorithm. Although the offline phase incurs  $O(\log N)$  depth per recursion depth, the offline work of all recursion depths can be performed concurrently rather than sequentially. On the other hand, the online phase of their routing algorithm must be performed sequentially among the recursion depths, but happily the online routing phase incurs only O(1) depth per recursion depth. Unfortunately, the offline/online routing algorithm of Chan et al. [7] is a randomized algorithm that leverages some form of statistical "load balancing", and such load balancing can fail with negligibly small probability — this makes their algorithm unsuitable for the perfect security setting.

We propose a novel offline/online routing algorithm that achieves *perfect* security using special expander graphs — our techniques can be viewed as a method for derandomizing a new variant of the offline/online routing techniques described by Chan et al. [7]. Like Chan et al. [7], our offline/online routing algorithm achieves  $O(\log N)$  depth for each recursion depth in the offline stage but the work in all recursion depths can be performed in parallel in the offline stage. By contrast, the online phase must traverse the recursion depths sequentially, but the online stage of routing can be accomplished in O(1) depth per recursion depth. To achieve this, we rely on a core building block called a "loose compactor". Leveraging special expander graphs, we show how to build a loose compactor with small online depth — since this part of our techniques are novel, we present a more expanded overview in Section 2.3 while deferring a detailed, formal description to later technical sections (Sections 6 and 7).

Reducing the depth of the maintain phase. We also must reduce the depth of the maintain phase. Although a naïve implementation of coordinated rebuild is to do it sequentially from recursion depth D down to recursion depth 0, we devise a method for performing the coordinated rebuild in parallel among all recursion depths. Recall that in the naïve solution, recursion depth d - 1 must wait for recursion depth d to relocate its blocks and be informed of the new position labels chosen before it starts reshuffling.

In our new algorithm, we introduce the notion of a rehearsal step called "mock shuffle" which determines the new positions of each of the blocks. Note that during this step, the newly chosen block contents (position labels) at the recursion depths are not available. Now, instead of sequentially performing the shuffle, in a mock shuffle, every recursion depth performs eager reshuffling without having updated the block's contents (recall that each block in recursion depth d is supposed to store position labels for the next recusion depth d + 1). After this mock shuffle, all blocks' new positions are determined though their contents are not known. Each mock reshuffle incurs  $O(\log N)$  depth, but they are independent and can be performed in parallel. At this moment, recursion depth d informs the newly chosen position labels to recursion depth d - 1 — now recursion depth d - 1 relies on oblivious routing to deliver each block's contents to the block. Note that recursion depth d - 1 has already chosen each block's position at this point and thus in this content update step, each block's

contents will be routed to the corresponding block and all blocks will maintain their chosen positions.

Using this idea, although each recursion depth incurs  $O(\log N)$  depth for the maintain phase, all recursion depths can now perform the maintain-phase operations in parallel.

Additional techniques. Besides the above, additional tricks are needed to achieve  $\widetilde{O}(\log N)$  depth. For example, within each recursion depth, all the hierarchical levels must be read in parallel during the fetch phase rather than sequentially like in existing hierarchical ORAMs [21, 22], and the result of these fetches can be aggregated using an oblivious select operation incurring  $O(\log \log N)$  depth (see Section 3.3). It is possible for us to read all the hierarchical levels in parallel since each recursion depth must have received the position labels of all real blocks requested before its fetch phase starts — and thus we know for each requested block which level to look for a real element and which level to visit dummies. We defer additional algorithmic details and tricks to the later technical sections.

### 2.3 Offline/Online Routing with Special Expander Graphs

Informal problem statement. Without going into excessive details, consider the following abstract problem: imagine that m CPUs at a parent depth have fetched m real or dummy blocks, and each real block contains two position labels for the next depth — thus in total up to 2m position labels have been fetched. Meanwhile, m CPUs at the next depth are waiting to receive m position labels before they can start their fetch. Our task is to obliviously route the (up to) 2m position labels at the parent depth to the m CPUs at the child depth. Using oblivious routing directly would incur  $\Omega(\log m)$  depth and thus is too expensive.

A blueprint: using an offline/online algorithm. As mentioned earlier, our highlevel idea is to leverage an offline-online paradigm such that the online phase, which must be performed sequentially for all recursion depths, should have small parallel runtime for each recursion depth.

Here is another idea: suppose that we are somehow able to compress the 2m position labels down to m, removing the ones that are not needed by the next recursion depth — this is in fact non-trivial but for now, suppose that somehow it can be accomplished.

Our plan is then the following: in the offline phase, we obliviously and randomly permute the *m* position labels to be routed (without leaking the permutation), and we obliviously compute the routing permutation  $\pi$  preserving the following invariant: the CPU at position  $\pi(i)$  (in the child depth) is waiting for the *i*-th position label in the permuted array. In other words, the *i*-th position label wants to be routed to the CPU in position  $\pi(i)$ ; and in the offline phase, we want to route down this  $\pi$ .

If we can accomplish all of the above, then in the online phase we simply apply the routing permutation that has been recorded and it takes a single parallel step to complete the routing. Moreover, for the offline phase, as long as we can perform the operations in parallel across all recursion depths, we are allowed to incur  $\log m$  depth.

Informally, obliviousness holds because of the following: recall that the m labels to be routed have been obliviously and randomly permuted. Now, although the routing permutation  $\pi$  is revealed in the online phase, the revealed permutation is uniform at random to an observer.

Technical challenges: compaction (and more). The above blueprint seems promising, but there are multiple technical challenges. One critical ingredient that is missing is how to perform compaction from 2m elements down to m, removing the labels not needed by the next recursion depth — in fact, even if we can solve this compaction problem, additional challenges remain in putting these techniques together. However, for the time being, let us focus on the compaction problem alone, leaving the remaining challenges to Sections 6 and 7. The most naïve method is again to leverage oblivious sorting but unfortunately that takes  $\Omega(\log m)$  depth and thus is too expensive for our purpose.

Pippenger's factory-facility problem. Our approach is inspired by the elegant techniques described by Pippenger in constructing a self-routing super-concentrator [36]. Pippenger's elegant construction can be used to solve a "factory-facility" problem described as follows. Suppose that 2m factories and m facilities form a special bipartite expander graph: each factory is connected to  $\mathfrak{d}$  facilities and each facility is connected to  $2\mathfrak{d}$  factories, where  $\mathfrak{d}$  is a constant. Among the factories, m/64 of them are productive and actually end up manufacturing products. Each productive factory produces  $\mathfrak{d}/2$  products; these products must be routed to a facility to be stored, and each facility has a storage capacity of  $\mathfrak{d}/2$ . Now, the question is: given the set of productive factories (and assuming that the bipartite graph is known), can we find a satisfying assignment for routing products to facilities, such that 1) every edge in the bipartite graph routes carries at most one unit of flow; 2) all products manufactured are routed; and 3) no facility exceeds its storage capacity.

In his ingenious work [36], Pippenger described a distributed protocol for finding such an assignment: imagine that the factories and facilities are Interactive Turing Machines. Now the factories and facilities exchange messages over edges in the bipartite graph. Pippenger's protocol completes after  $O(\log m)$  rounds of interaction and a total of O(m) number of messages. Pippenger proved that as long as the underlying bipartite graph satisfies certain expansion properties, his protocol is guaranteed to find a satisfying assignment.

Using Pippenger's protocol for oblivious loose compaction. Now we can reduce the problem of (loose) compaction to Pippenger's factory-facility problem. Imagine that there are twice as many factories as there are facilities. Another way to think of the factory-facility problem is the following: imagine that the factories initially store real elements (i.e., the manufactured products) as well as dummies, and in total  $2m \cdot (\mathfrak{d}/2)$  amount of storage is consumed since each factory can produce at most  $\mathfrak{d}/2$  products. We ensure that only m/64 factories are

productive by appropriately adding a constant factor of dummy elements (i.e., dummy factories and facilities). Now, when routed to the facilities, the storage amount is compressed down by a factor of 2 since each facility can store up to  $\mathfrak{d}/2$  products and the number of facilities is half that of factories. Further, for any satisfying assignment, we guarantee that no real element is lost during the routing, and that is why the compaction algorithm satisfies correctness. Note that such compaction is *loose*, i.e., we do not completely remove dummies during compaction although we do cut down total storage by a half while preserving all real elements. In our OPRAM algorithm, it turns out that such *loose* compaction is sufficient, since CPUs who have received dummy position labels can always perform dummy fetch operations.

Pippenger's protocol can be easily simulated on a PRAM incurring O(m) total work and  $O(\log m)$  parallel runtime — however, a straightforward PRAM simulation of their protocol is *not* oblivious. In particular, the communication patterns between the factories and facilities (which translate to memory access patterns when simulated on a PRAM) leak information about which factories are productive. Thus it remains for us to show how to *obliviously* simulate his protocol on a PRAM. We show that this can be done incurring  $O(m \log m)$  total work and  $O(\log m)$  parallel runtime — note that the extra log m overhead arises from the obliviousness requirement.

Finally, we apply the loose compaction algorithm in an offline/online fashion too. In the offline phase, we execute Pippenger's protocol obliviously on a PRAM to compute the satisfying assignment — the offline phase can be parallelized over all recursion depths, thus incurring  $O(\log m)$  parallel runtime overall. In the online phase, we only have to carry out the satisfying assignment that has already been recorded in the offline phase to perform the actual routing of the fetched position labels, and this can be accomplished in O(1) online parallel runtime.

We defer a detailed description of the techniques to the formal technical sections.

### 3 Definitions

### 3.1 Parallel Random-Access Machines

We review the concepts of a parallel random-access machine (PRAM) and an oblivious parallel random-access machine (OPRAM). Some of the definitions in this section are borrowed verbatim from Boyle et al. [6] or Chan and Shi [9].

Although we give definitions only for the parallel case, we point out that this is without loss of generality, since a sequential RAM can be thought of as a special case PRAM with one CPU.

Parallel Random-Access Machine (PRAM). A parallel random-access machine consists of a set of CPUs and a shared memory denoted by mem indexed by the address space  $\{0, 1, \ldots, N-1\}$ , where N is a power of 2. In this paper, we refer to each memory word also as a *block*, which is at least  $\Omega(\log N)$  bits long.

In a PRAM, each step of the execution can employ multiple CPUs, and henceforth we use  $m_t$  to denote the number of CPUs involved in executing the *t*-th step for  $t \in \mathbb{N}$ . In each step, each CPU executes a next instruction circuit denoted  $\Pi$ , updates its CPU state; and further, CPUs interact with memory through request instructions  $\mathbf{I}^{(t)} := (I_i^{(t)} : i \in [m_t])$ . Specifically, at time step t, CPU *i*'s instruction is of the form  $I_i^{(t)} := (\text{read}, \text{addr})$ , or  $I_i^{(t)} := (\text{write}, \text{addr}, \text{data})$ where the operation is performed on the memory block with address addr and the block content data.

If  $I_i^{(t)} = (\text{read}, \text{addr})$  then the CPU *i* should receive the contents of mem[addr] at the beginning of time step *t*. Else if  $I_i^{(t)} = (\text{write}, \text{addr}, \text{data})$ , CPU *i* should still receive the contents of mem[addr] at the beginning of time step *t*; further, at the end of step *t*, the contents of mem[addr] should be updated to data.

Write conflict resolution. By definition, multiple read operations can be executed concurrently with other operations even if they visit the same address. However, if multiple concurrent write operations visit the same address, a conflict resolution rule will be necessary for our PRAM to be well-defined. In this paper, we assume the following:

- The original PRAM supports concurrent reads and concurrent writes (CRCW) with an arbitrary, parametrizable rule for write conflict resolution. In other words, there exists some priority rule to determine which write operation takes effect if there are multiple concurrent writes in some time step t.

- Our compiled, oblivious PRAM (defined below) is a "concurrent read, exclusive write" PRAM (CREW). In other words, our OPRAM algorithm must ensure that there are no concurrent writes at any time.

We note that a CRCW-PRAM with a parametrizable conflict resolution rule is among the most powerful CRCW-PRAM model, whereas CREW is a much weaker model. Our results are stronger if we allow the underlying PRAM to be more powerful but our compiled OPRAM uses a weaker PRAM model. For a detailed explanation on how stronger PRAM models can emulate weaker ones, we refer the reader to the work by Hagerup [26].

*CPU-to-CPU communication.* In the remainder of the paper, we sometimes describe our algorithms using CPU-to-CPU communication. For our OPRAM algorithm to be oblivious, the inter-CPU communication pattern must be oblivious too. We stress that such inter-CPU communication can be emulated using shared memory reads and writes. Therefore, when we express our performance metrics, we assume that all inter-CPU communication is implemented with shared memory reads and writes. In this sense, our performance metrics already account for any inter-CPU communication, and there is no need to have separate metrics that characterize inter-CPU communication. In contrast, some earlier works [10] adopt separate metrics for inter-CPU communication.

Additional assumptions and notations. Henceforth, we assume that each CPU can only store O(1) memory blocks. Further, we assume for simplicity that the runtime T of the PRAM is fixed a priori and publicly known. Therefore, we can consider a PRAM to be parametrized by the following tuple

$$\mathsf{PRAM} := (\Pi, N, T, m_1, m_2, \dots, m_T),$$

where  $\Pi$  denotes the next instruction circuit, N denotes the total memory size (in terms of number of blocks), T denotes the PRAM's total runtime, and  $m_t$ denotes the number of CPUs in the t-th step for  $t \in [T]$ .

Finally, in this paper, we consider PRAMs that are *stateful* and can evaluate a sequence of inputs, carrying state in between. Without loss of generality, we assume each input can be stored in a single memory block.

### 3.2 Oblivious Parallel Random-Access Machines

An OPRAM is a (randomized) PRAM with certain security properties, i.e., its access patterns leak no information about the inputs to the PRAM.

*Randomized PRAM.* A *randomized PRAM* is a PRAM where the CPUs are allowed to generate private random numbers. For simplicity, we assume that a randomized PRAM has a priori known, deterministic runtime, and that the CPU activation pattern in each time step is also fixed a priori and publicly known.

*Memory access patterns.* Given a PRAM program denoted PRAM and a sequence inp of inputs, we define the notation Addresses[PRAM](inp) as follows:

- Let T be the total number of parallel steps that PRAM takes to evaluate inputs inp.

- Let  $A_t := (\mathsf{addr}_1^t, \mathsf{addr}_2^t, \dots, \mathsf{addr}_{m_t}^t)$  be the list of addresses such that the *i*th CPU accesses memory address  $\mathsf{addr}_i^t$  in time step *t*.

- We define Addresses[PRAM](inp) to be the random object  $[A_t]_{t \in [T]}$ .

Oblivious PRAM (OPRAM). We say that a PRAM is perfectly oblivious, iff for any two input sequences  $inp_0$  and  $inp_1$  of equal length, it holds that the following distributions are identically distributed (where  $\equiv$  denotes identically distributed):

$$\mathsf{Addresses}[\mathsf{PRAM}](\mathsf{inp}_0) \equiv \mathsf{Addresses}[\mathsf{PRAM}](\mathsf{inp}_1)$$

We remark that for statistical and computational security, some earlier works [8, 9] presented an adaptive, composable security notion. The perfectly oblivious counterpart of their adaptive, composable notion is equivalent to our notion defined above. In particular, our notion implies security against an adaptive adversary who might choose the input sequence inp adaptively over time after having observed partial access patterns of PRAM.

We say that OPRAM is a *perfectly oblivious simulation* of PRAM iff OPRAM is perfectly oblivious, and moreover OPRAM(inp) is identically distributed as PRAM(inp) for any input inp. In the remainder of the paper, we always assume that the original PRAM has a fixed number of CPUs (denoted m) in all steps of execution. For the compiled OPRAM, we consider two models 1) when the OPRAM always consumes exactly m CPUs in every step (i.e., the same number of CPUs as the original PRAM); and 2) when the OPRAM can consume an unbounded number of CPUs in every step; in this case, the actual number of CPUs consumed in each step may vary. We leave it as an open problem how to obliviously simulate a PRAM with a varying number of CPUs (without naïvely padding the number of CPUs to the maximum which can incur large overhead).

Oblivious simulation metrics. We adopt the following metrics to characterize the overhead of (parallel) oblivious simulation of a PRAM. In the following, when we say that an OPRAM scheme consumes T parallel steps (or W total work), we mean that the OPRAM scheme consumes T parallel steps (or W total work) except with negligible in N probability. In other words, the definition of our metrics allows the OPRAM to sometimes, but with negligibly small (in N) probability, exceed the desired runtime or total work bound; however, note that the security or correctness failure probability must be 0<sup>10</sup>.

- <u>Simulation overhead</u> (when the OPRAM consumes the same number of CPUs as the PRAM). If a PRAM that consumes m CPUs and completes in T parallel steps can be obliviously simulated by an OPRAM that completes in  $\gamma \cdot T$  steps also with m CPUs (i.e., the same number of CPUs as the original PRAM), then we say that the simulation overhead is  $\gamma$ . Note that this means that every PRAM step is simulated by on average  $\gamma$  OPRAM steps.

- <u>Total work blowup</u> (when the OPRAM may consume unbounded number of  $\overline{CPUs}$ ). A PRAM's total work is the number of steps necessary to simulate the PRAM under a single CPU, and is equal to the sum  $\sum_{t \in [T]} m_t$ . If a PRAM of total work W can be obliviously simulated by an OPRAM of total work  $\gamma \cdot W$  we say that the total work blowup of the oblivious simulation is  $\gamma$ .

- <u>Depth blowup</u> (when the OPRAM may consume unbounded number of CPUs). A PRAM's depth is defined to be its parallel runtime when there are an unbounded number of CPUs. If a PRAM of depth D can be obliviously simulated by an OPRAM of depth  $\gamma \cdot D$  we say that the depth blowup of the oblivious simulation is  $\gamma$ .

Note that the simulation overhead is a good standalone metric if we assume that the OPRAM must consume the same number of CPUs as the PRAM. If the OPRAM is allowed to consume more CPUs than the PRAM, we typically use the metrics total work blowup and depth blowup in conjunction with each other: total work blowup alone does not characterize how much the OPRAM

<sup>&</sup>lt;sup>10</sup> Similarly, the perfectly secure ORAM by Damgård et al. [12] also allowed a negligible small probability for the algorithm to exceed the desired complexity bound but the security or correctness failure probability must be 0.

preserves parallelism; and depth blowup alone does not capture the extent to which the OPRAM preserves total work.

Finally, the following simple fact is useful for understanding the complexity of (oblivious) parallel algorithms.

**Fact 2** Let C > 1. If an (oblivious) parallel algorithm can complete in T steps consuming m CPUs, then it can complete in CT steps consuming  $\lceil \frac{m}{C} \rceil$  CPUs.

### 3.3 Building Blocks

We now introduce several useful oblivious building blocks. With the exception of oblivious random permutation, we assume that all remaining building blocks are deterministic: for a deterministic algorithm, obliviousness means that the algorithm's memory access pattern is independent of its input.

Oblivious sort. Ajtai, Komlós, and Szemerédi [1] show how to construct a circuit with  $n \log n$  comparators that can correctly sort any input sequence containing n comparable elements. This immediately gives rise to a parallel oblivious sorting algorithm with  $O(n \log n)$  total work and  $O(\log n)$  depth.

Oblivious routing. Oblivious routing solves the following problem. Suppose n source CPUs each holds a data block with a distinct key (or a dummy block). Further, n destination CPUs each holds a key and requests a data block identified by its key — multiple destination CPUs can possibly request the same key. An oblivious routing algorithm routes the requested data block to the destination CPU in an oblivious manner. We may assume that the destination CPUs are represented by an ordered array X. Initially the payload of each entry of X is left empty. After the routing, each entry of X receives a data block (the received data block is dummy if no source CPUs hold the same key as requested). The ordering of elements in X is preserved between the input and output.

Boyle et al. [6] showed that through a combination of oblivious sorts and oblivious aggregation, oblivious routing can be achieved in  $O(\log n)$  parallel runtime with O(n) CPUs.

Obliviously computing the routing permutation. Suppose that we are given a source array src of length n where each entry holds a distinct key, and a destination array dst also of length n where each entry holds a distinct key. Further, it is guaranteed that the set of keys in src is the same as the set of keys in dst. We would like to write down a permutation  $\pi$  (henceforth referred to as the routing permutation) such that applying  $\pi$  to src would result in the same order of keys as dst. The recent work by Chan and Shi [9] showed how to implement the above task obliviously using O(1) number of oblivious sorts. Thus, with O(n) CPUs the routing permutation can be computed in  $O(\log n)$  parallel runtime.

Oblivious select. Consider the following problem: given a set of n elements among which at most one element is distinguishing, output the distinguishing element (and if no element is distinguishing, output  $\perp$ ). It is not difficult to see that by building an aggregation tree over the n elements, one can accomplish oblivious select with n CPUs in log n parallel steps.

Oblivious prefix sum. Given an array X of length n, every  $i \in [n]$  wants to compute the sum of the prefix X[1..i]. There exists a parallel oblivious algorithm to achieve this in  $O(\log n)$  steps consuming n CPUs [27].

Oblivious random permutation. Let ORP be an algorithm that upon receiving an input array X, outputs a permutation of X. Let  $\mathcal{F}_{perm}$  denote an ideal functionality that upon receiving the input array X, outputs a perfectly random permutation of X.

We say that ORP is a *perfectly oblivious* random permutation, iff there exists a simulator Sim such that the joint distribution  $(\mathcal{F}_{\text{perm}}(X), \text{Sim}(|X|))$  is identically distributed as the joint distribution of the output and the addresses incurred by running ORP on X. Note that the simulator Sim is given only the input length |X| but not the contents of X.

Chan, Chung, and Shi [7] recently describe a perfectly oblivious random permutation algorithm, which, except with negligible in  $\lambda$  probability, completes in  $O(\log n)$  parallel steps consuming n CPUs assuming each block is large enough to store  $\log \lambda$  bits. We summarize their construction in the following theorem:

**Theorem 3 (Perfectly oblivious random permutation** [7]). Assume that each memory block is large enough to store at least  $\log \lambda$  bits and that  $n \leq \lambda \leq 2^{O(n^2)}$ . Then, there exists a perfectly oblivious random permutation algorithm that consumes n CPUs. Except with negligible in  $\lambda$  probability, the algorithm completes in  $O(\log n)$  parallel steps and  $O(n \log n)$  work.

We note that the failure is in terms of the algorithm's runtime — there is a negligibly small probability that the algorithm will run for longer, but the algorithm guarantees perfect security regardless.

### 4 Parallel One-Time Oblivious Memory

We define and construct an abstract datatype to process non-recurrent memory lookup requests. Although the abstraction is similar to the oblivious hashing scheme in Chan et al. [8], our one-time memory scheme needs to be perfectly secure and does not use a hashing scheme. Furthermore, we assume that every real lookup request is *tagged with a correct position label* that indicates where the requested block is — in this section, we simply assume that the correct position labels are simply provided during lookup; but later in our full OPRAM scheme, we will use a recursive ORAM/OPRAM technique reminiscent of those used in binary-tree-based ORAM/OPRAM schemes [9, 11, 39, 41, 42] such that we can obtain the position label of a block first before fetching the block.

### 4.1 Definition: One-Time Oblivious Memory

Intuition. We describe the intuition using the *sequential* special case but our formal presentation later will directly describe the parallel version. An oblivious one-time memory supports three operations: 1) Build, 2) Lookup, and 3) Getall. Build is called once upfront to create the data structure: it takes in a set of real blocks (each tagged with its logical address) and creates a data structure that facilitates lookup. After this data structure is created, a sequence of lookup operations can be performed: each lookup can request a real block identified by its logical address or a dummy block denoted  $\perp$  — if the requested block is a real block, we assume that the correct position label is supplied to indicate where in the data structure the requested block is. Finally, when the data structure is no longer needed, one may call a Getall operation to obtain a list of blocks (tagged with their logical addresses) that have not been looked up yet — in our OPRAM scheme later, this is the set of blocks that need to be preserved during rebuilding.

We require that our oblivious one-time memory data structure retain obliviousness as long as 1) the sequence of real blocks looked up all exist in the data structure (i.e., it appeared as part of the input to Build), and moreover, each logical address is looked up at most once; and 2) at most  $\tilde{n}$  number of dummy lookups may be made where  $\tilde{n}$  is a predetermined parameter (that the scheme is parametrized with).

Formal Definition Our formal presentation will directly describe the parallel case. In the parallel version, lookup requests come in batches of size m > 1.

A (parallel) one-time memory scheme denoted  $\mathsf{OTM}^{[n,m,t]}$  is parametrized by three parameters: n denotes the upper bound on the number of real elements; m is the batch size for lookups; t is the upper bound on the number of batch lookups supported. We use three parameters because we use different versions of  $\mathsf{OTM}$ . For the basic version in Section 5, we have  $t = \frac{n}{m}$  number of batch lookups, whereas in Section 7, the number of batch lookups is larger (which means that some of the lookup addresses must be dummy).

The (parallel) one-time memory scheme  $\mathsf{OTM}^{[n,m,t]}$  is comprised of the following possibly randomized, stateful algorithms to be executed on a *Concurrent-Read, Exclusive-Write* PRAM — note that since the algorithms are stateful, every invocation will update an implicit data structure in memory. Henceforth we use the terminology key and value in the formal description but in our OPRAM scheme later, a real key will be a logical memory address and its value is the block's content.

$- U \leftarrow \mathsf{Build}(\{(k_i, v_i) : i \in [n]\})$ : given a set of n key-value pairs  $(k_i, v_i)$ , where each pair is either real or of the form  $(\bot, \bot)$ , the Build algorithm creates an implicit data structure to facilitate subsequent lookup requests, and moreover outputs a list U of exactly n key-position pairs where each pair is of the form  $(k, \mathsf{pos})$ . Further, every real key input to Build will appear exactly once in the list U; and the list U is padded with  $\bot$  to a length n. Note that U does not include the values  $v_i$ 's. Later in our scheme, this key-position list U will be propagated back to the parent recursion depth during a coordinated rebuild<sup>11</sup>.

- $(v_i : i \in [m])$  ← Lookup({ $(k_i, pos_i) : i \in [m]$ }): there are *m* concurrent Lookup operations in a single batch, where we allow each key  $k_i$  requested to be either real or  $\bot$ . Moreover, in each batch, at most n/t of the keys are real.

- $R \leftarrow$  Getall: the Getall algorithm returns an array R of length n where each entry is either  $\perp$  or real and of the form (k, v). The array R should contain all real entries that have been inserted during Build but have not been looked up yet, padded with  $\perp$  to a length of n.

Valid request sequence. Our oblivious one-time memory ensures obliviousness only if lookups are non-recurrent (i.e., never look for the same real key twice); and moreover the number of lookups requests must be upper bounded by a predetermined parameter. More formally, a sequence of operations is valid, iff the following holds:

- The sequence begins with a single call to Build upfront; followed by a sequence of at most t batch Lookup calls, each of which supplies a batch of m keys and the corresponding position labels; and finally the sequence ends with a single call to Getall.

- The Build call is supplied with an input array  $S := \{(k_i, v_i)\}_{i \in [n]}$ , such that any two real entries in S must have distinct keys.

- For every  $\mathsf{Lookup}(\{(k_i, \mathsf{pos}_i) : i \in [m]\})$  query in the sequence, if each  $k_i$  is a real key, then  $k_i$  must be contained in S that was input to Build earlier. In other words,  $\mathsf{Lookup}$  requests are not supposed to ask for real keys that do not exist in the data structure<sup>12</sup>; moreover, each  $(k_i, \mathsf{pos}_i)$  pair supplied to  $\mathsf{Lookup}$  must exist in the U array returned by the earlier invocation of Build, i.e.,  $\mathsf{pos}_i$  must be a correct position label for  $k_i$ ; and

- Finally, in all Lookup requests in the sequence, no two keys requested (either in the same or different batches) are the same.

*Correctness.* Correctness requires that

for any valid request sequence, with probability 1, for every Lookup({(k<sub>i</sub>, pos<sub>i</sub>) : i ∈ [m]}) request, the *i*-th answer returned must be ⊥ if k<sub>i</sub> = ⊥; else if k<sub>i</sub> ≠ ⊥, Lookup must return the correct value v<sub>i</sub> associated with k<sub>i</sub> that was input to the earlier invocation of Build.

<sup>12</sup> We emphasize this is a major difference between this one-time memory scheme and the oblivious hashing abstraction of Chan et al. [8]); Chan et al.'s abstraction [8] allows lookup queries to ask for keys that do not exist in the data structure.

<sup>&</sup>lt;sup>11</sup> Note that we do not explicitly denote the implicit data structure in the output of Build, since the implicit data structure is needed only internally by the current oblivious one-time memory instance. In comparison, U is explicitly output since U will later on be (externally) needed by the parent recursion depth in our OPRAM construction.

- 22 T-H. Hubert Chan, Kartik Nayak, and Elaine Shi

- 2. for any valid request sequence, with probability 1, Getall must return an array R containing every (k, v) pair that was supplied to Build but has not been looked up; moreover the remaining entries in R must all be  $\perp$ .

*Perfect obliviousness.* We say that two valid request sequences are *length-equivalent*, if the input sets to Build have equal size, and the number of Lookup requests (where each request asks for a batch of m keys) in the two sequences are the same.

We say that a (parallel) one-time memory scheme is perfectly oblivious, iff for any two length-equivalent request sequences that are valid, the distribution of access patterns resulting from the algorithms are *identically distributed*.

### 4.2 Construction

**Intuition.** We first explain the intuition for the sequential case, i.e., m = 1. The intuition is simply to permute all elements received as input during Build. However, since subsequent lookup requests may be dummy (also denoted  $\perp$ ), we also need to pad the array with sufficiently many dummies to support these lookup requests. The important invariant is that each real element as well as each dummy will be accessed at most once during lookup requests. For reals, this is guaranteed since the definition of a valid request sequence requires that each real key be requested no more than once, and that each real key requested must exist in the data structure. For dummies, every time a  $\perp$ -request is received, we always look for an unvisited dummy. To implement this idea, one tricky detail is that unlike real lookup requests, dummy requests do not carry the position label of the next dummy to be read — thus our data structure itself must maintain an oblivious linked list of dummies such that we can easily find out where the next dummy is. Since all real and dummies are randomly permuted during Build, and due to the aforementioned invariant, every lookup visits a completely random location of the data structure thus maintaining perfect obliviousness.

It is not too difficult to make the above algorithm parallel (i.e., for the case m > 1). To achieve this, one necessary modification is that instead of maintaining a single dummy linked list, we now must maintain m dummy linked lists. These m dummy linked lists are created during Build and consumed during Lookup.

**Detailed Construction.** At the end of Build, our algorithm creates an inmemory data structure consisting of the following:

- 1. An array A of length  $n + \tilde{n}$ , where  $\tilde{n} := tm$  denotes the number of dummies and n denotes the number of real elements. Each entry of the array A (real or dummy alike) has four fields (key, val, next, pos) where

- key is a key that is either real or dummy; and val is a value that is either real or dummy.

- the field  $next \in [0..n + \tilde{n})$  matters only for dummy entries, and at the end of the Build algorithm, the next field stores the position of the next entry in the dummy linked list (recall that all dummy entries form *m* linked lists); and

- the field  $\mathsf{pos} \in [0..n + \tilde{n})$  denotes where in the array an entry finally wants to be — at the end of the Build algorithm it must be that  $A[i].\mathsf{pos} = i$ . However, during the algorithm, entries of A will be permuted transiently; but as soon as each element i has decided where it wants to be (i.e.,  $A[i].\mathsf{pos})$ , it will always carry its desired position around during the remainder of the algorithm.

- 2. An array that stores the head pointers of all m dummy linked lists. Specifically, we denote the m head pointers as  $\{dpos_i : i \in [m]\}$  where each  $dpos_i \in [0..n + \tilde{n})$  is the head pointer of one dummy linked list.

These in-memory data structures, including A and the dummy pointers will then be updated during Lookup.

<u>Build.</u> Our oblivious  $\mathsf{Build}(\{(k_i, v_i)\}_{i \in [n]})$  algorithm proceeds as follows.

1. Initialize. Construct an array A of length  $n + \tilde{n}$  whose entries are of the form described above. Specifically, the keys and values for the first n entries of A are copied from the input. Recall that the input may contain dummies too, and we use  $\perp$  to denote a dummy key from the input.

The last  $\tilde{n}$  entries of A contain *special* dummy keys that are numbered. Specifically, for each  $i \in [1..\tilde{n}]$ , we denote  $A_n[i] := A[n-1+i]$ , and the entry stored at  $A_n[i]$  has key  $\perp_i$  and value  $\perp$ .

- 2. Every element decides at random its desired final position. Specifically, perform a perfectly oblivious random permutation on the entries of A this random permutation decides where each element finally wants to be. Now, for each  $i \in [0..n+\tilde{n})$ , let A[i].pos := i. At this moment, A[i].pos denotes where the element A[i] finally wants to be. Henceforth in the algorithm, the entries of A will be moved around but each element always carries around its desired final position.

- 3. Construct the key-position map U. Perform oblivious sorting on A using the field key. We assume that real keys have the highest priority followed by  $\perp < \perp_1 < \cdots < \perp_{\widetilde{n}}$  (where smaller keys come earlier).

At this moment, we can construct the key-position map U from the first n entries of A — recall that each entry of U is of the form (k, pos).

4. Construct m dummy linked lists. Observe that the last  $\tilde{n}$  entries of A contain special dummy keys, on which we perform the following to build m disjoint singly-linked lists (each of which has length t). For each  $i \in [1..\tilde{n}]$ , if  $i \mod t \neq 0$  we update the entry  $A_n[i]$ .next :=  $A_n[i+1]$ .pos, i.e., each dummy entry (except the last entry of each linked list) records its next pointer. We next record the positions of the heads of the m lists. For each  $i \in [m]$ , we

set  $dpos_i := A_n[t(i-1)]$ .pos.

5. Move entries to their desired positions. Perform an oblivious sort on A, using the fourth field **pos**. (This restores the ordering according to the previous random permutation.)

At this moment, the data structure  $(A, \{dpos_i : i \in [m]\})$  is stored in memory. The key-position map U is explicitly output and later in our OPRAM scheme it will be passed to the parent recursion depth during coordinated rebuild. **Fact 4** Consuming  $O(\tilde{n} + n)$  CPUs and setting  $(\tilde{n} + n)^2 \leq \lambda \leq 2^{\tilde{n}+n}$ , the Build algorithm completes in  $O(\log(\tilde{n} + n))$  parallel steps, except with probability negligible in  $\lambda$ .

*Proof.* Observe that the algorithm's cost is dominated by O(1) number of oblivious sorts which can be realized with the AKS sorting network [1].

Moreover, the algorithm incurs one application of oblivious random permutation, whose performance is stated in Theorem 3.

Lookup. We implement a batch of m concurrent lookup operations {Lookup({ $(k_i, pos_i) : i \in [m]$ }) as follows. For each  $i \in [m]$ , we perform the following in parallel.

- 1. Decide position to fetch from. If  $k_i \neq \bot$  is real, set  $pos := pos_i$ , i.e., we want to use the position label supplied from the input. Else if  $k_i = \bot$ , set  $pos := dpos_i$ , i.e., the position to fetch from is the next dummy in the *i*-th dummy linked lists. (To ensure obliviousness, the algorithm can always pretend to execute both branches of the if-statement.) At this moment, **pos** is the position to fetch from (for the *i*-th request out of *m* concurrent requests).

- 2. Read and remove. Read the value from A[pos] and mark  $A[pos] := \bot$ .

- Update dummy head pointer if necessary. If pos = dpos<sub>i</sub>, update the dummy head pointer dpos<sub>i</sub> := next. (To ensure obliviousness, the algorithm can pretend to modify dpos<sub>i</sub> in any case.)

- 4. Return. Return the value read in the above Step 2.

The following fact is straightforward from the description of the algorithm.

**Fact 5** The Lookup algorithm completes in O(1) parallel steps with O(m) CPUs.

<u>Getall.</u> Getall is implemented by the following simple procedure: obliviously sort A by the key such that all real entries are packed in front. Return the first n entries of the resulting array (and removing the metadata entries next and pos in the result).

**Fact 6** The Getall algorithm completes in  $\log(\tilde{n} + n)$  parallel steps consuming  $O(\tilde{n} + n)$  CPUs.

*Proof.* Straightforward by observing that the algorithm's cost is dominated by O(1) number of oblivious sorts which can be realized with the AKS sorting network [1].

Lemma 1 (Perfect obliviousness of the one-time memory scheme). The above (parallel) one-time memory scheme satisfies perfect obliviousness.

*Proof.* It suffices to prove that for any valid request sequence, the memory access patterns are identically distributed as those output by the following simulator that knows only n, m and the number of Lookup requests in the sequence.

First, almost all parts of Build are deterministic and data oblivious and thus the algorithm's access patterns can be simulated in the most straightforward fashion. The only randomized part of access patterns for Build is due to the oblivious random permutation. To simulate this part, the simulator calls the oblivious random permutation's simulator algorithm.

Second, to simulate the access patterns of Lookup, the simulator would read the memory location storing  $dpos_i$  for every  $i \in [m]$ . Then, it reads a random unread index of the array A and writes to it once too. Finally, it writes to  $dpos_i$ for every  $i \in [m]$ .

Third, simulating the access patterns of Getall is done in the most natural manner since Getall is deterministic.

It is not difficult to see that the real-world access patterns are identically distributed as the simulated ones due to the definition of oblivious random permutation (see Section 3.3) Particularly, observe that the above way of simulating the access patterns of Build is the same in nature as if we randomly permuted the data structure A upfront by a random permutation, (that is chosen independently from the simulated access patterns), then every real element and  $\perp_i$  will be in a random location. Note also that as long as no two real keys requested collide and every real key requested exists in the data structure A, then the real-world algorithm accesses each real or  $\perp_i$  element at most once, and thus every real-world access visits a random position of the array A (besides reading and writing {dpos<sub>i</sub> :  $i \in [m]$ }).

Summarizing the above, we conclude with the following theorem.

**Theorem 7 (One-time oblivious memory).** Let  $\lambda \in \mathbb{N}$  be a parameter related to the probability that the algorithm's runtime exceeds a desired bound. Assume that each memory block can store at least  $\log n + \log \lambda$  bits. There exists a perfectly oblivious one-time scheme such that Build takes  $O(\log n)$  parallel steps (except with negligible in  $\lambda$  probability) consuming n CPUs, Lookup for a batch of m requests takes O(1) parallel steps consuming m CPUs, and Getall takes  $O(\log n)$  parallel steps consuming n CPUs.

# 5 Basic OPRAM with $O(\log^3 N)$ Simulation Overhead

Recall that N denotes the number of logical memory blocks consumed by the original PRAM, and each memory block can store at least  $\Omega(\log N)$  bits. For clarity, in this section, we will first describe an OPRAM construction such that each batch of m memory requests takes  $O(\log^3 N)$  parallel steps to satisfy with m CPUs. Later in Section 7, we will describe how to further parallelize the OPRAM when the OPRAM can consume more CPUs than the original PRAM.

*Roadmap.* We briefly explain the technical roadmap of this section:

- In Section 5.1, we will first describe a *position-based OPRAM* that supports two operations: Lookup and Shuffle. A position-based OPRAM is an almost

fully functional OPRAM scheme except that every real lookup request must supply a correct position label. In our OPRAM construction, these position labels will have been fetched from small recursion depths and therefore will be ready when looking up the position-based OPRAM.

Our position-based OPRAM relies on the hierarcial structure proposed by Goldreich and Ostrovsky [21,22], as well as techniques by Chan et al. [8] that showed how to parallelize such a hierarchical framework.

In Section 5.2, we explain how to leverage "coordinated rebuild" and recursion techniques to build a recursive OPRAM scheme that composes logarithmically many instances of our position-based OPRAM, of geometrically decreasing sizes.

### 5.1 Position-Based OPRAM

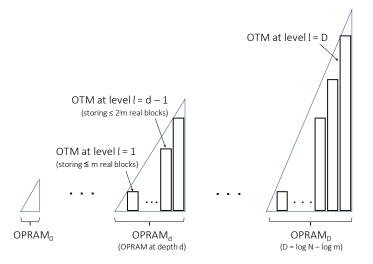

Our basic OPRAM scheme (Section 5.2) will consist of logarithmically many position-based OPRAMs of geometrically increasing sizes, henceforth denoted OPRAM<sub>0</sub>, OPRAM<sub>1</sub>, OPRAM<sub>2</sub>, ..., OPRAM<sub>D</sub> where  $D := \log_2 N - \log_2 m$ . Specifically, OPRAM<sub>d</sub> stores  $\Theta(2^d \cdot m)$  blocks where  $d \in \{0, 1, \ldots, D\}$ . The last one OPRAM<sub>D</sub> stores the actual data blocks whereas every other OPRAM<sub>d</sub> where d < D recursively stores the position labels for the next depth d + 1.

**Data Structure.** As we shall see, the case  $\mathsf{OPRAM}_0$  is trivial and is treated specially at the end of this section (Section 5.1). Below we focus on describing  $\mathsf{OPRAM}_d$  for some  $1 \leq d \leq D = \log N - \log m$ . For  $d \neq 0$ , each  $\mathsf{OPRAM}_d$  consists of d + 1 levels geometrically growing in size, where each level is a one-time oblivious memory scheme as defined and described in Section 4. We specify this data structure more formally below.

*Hierarchical levels.* The position-based  $\mathsf{OPRAM}_d$  consists of d+1 levels henceforth denoted as  $(\mathsf{OTM}_j : j = 0, \ldots, d)$  where level j is a one-time oblivious memory scheme,